The documentation and process conversion measured necessary to comply with this revision shall be completed by 3 July 2012.

INCH-POUND

MIL-STD-750-3

3 January 2012

SUPERSEDING

MIL-STD-750E (IN PART)

20 November 2006

(see 6.4)

## DEPARTMENT OF DEFENSE

## **TEST METHOD STANDARD**

# TRANSISTOR ELECTRICAL TEST METHODS FOR SEMICONDUCTOR DEVICES

PART 3: TEST METHODS 3000 THROUGH 3999

AMSC N/A FSC 5961

### **FOREWORD**

- 1. This standard is approved for use by all Departments and Agencies of the Department of Defense.

- 2. This revision has resulted in many changes to the format, but the most significant one is the splitting the document into parts. See MIL–STD–750 for the change summary.

- 3. Comments, suggestions, or questions on this document should be addressed to: Commander, Defense Logistics Agency, DLA Land and Maritime, ATTN: VAC, P.O. Box 3990, Columbus, OH 43218–3990, or emailed to semiconductor@dla.mil. Since contact information can change, you may want to verify the currency of this address information using the ASSIST Online database at https://assist.daps.dla.mil.

| <u>PA</u> | <u>ARAGRAPH</u> <u>PA</u> |                                          |         |

|-----------|---------------------------|------------------------------------------|---------|

| FO        | REWO                      | RD                                       | ii      |

|           |                           |                                          |         |

|           | 1                         | SCOPE                                    |         |

|           | 1.1                       | Purpose                                  | 1       |

|           | 1.2                       | Numbering system                         | 1       |

|           | 1.2.1                     | Classification of tests                  | 1       |

|           | 1.2.2                     | Test method revisions                    | 1       |

|           | 1.3                       | Methods of reference                     | 1       |

|           | 2                         | APPLICABLE DOCUMENTS                     | 2       |

|           | 2.1                       | General                                  |         |

|           | 2.2                       | Government documents                     |         |

|           | 2.2.1                     | Specifications, standards, and handbooks |         |

|           | 2.3                       | Non-Government publications              |         |

|           | 2.4                       | Order of precedence                      |         |

|           | 2. 1                      |                                          |         |

|           | 3                         | DEFINITIONS                              | 4       |

|           | 3.1                       | Acronyms, symbols, and definitions       | , 1<br> |

|           | 3.2                       | Acronyms used in this standard           |         |

|           | 0.2                       |                                          |         |

|           | 4.                        | GENERAL REQUIREMENTS                     | 5       |

|           | 4.1                       | General                                  | 5       |

|           | 4.2                       | Test circuits                            |         |

|           | 4.4                       | Non-destructive tests                    | 5       |

|           | 4.4                       | Destructive tests                        | 5       |

|           | 4.5                       | Laboratory suitability                   | 5       |

|           | 4.0                       | Laboratory Suitability                   |         |

|           | 5.                        | DETAILED REQUIREMENTS                    | 5       |

|           | J.                        | DETAILED REQUIREMENTO.                   |         |

|           | 6.                        | NOTES                                    | 6       |

|           | 6.1                       | Intended use                             | 6       |

|           | 6.2                       | International standardization agreement  | 6       |

|           | 6.3                       | Subject term (key word) listing          | 6       |

|           | 6.4                       | Supersession data                        | 6       |

|           | U. <del>T</del>           | Oupersossion data                        |         |

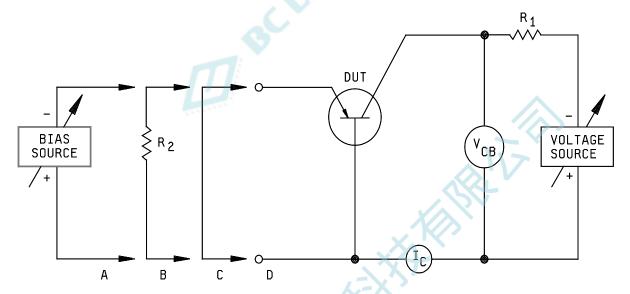

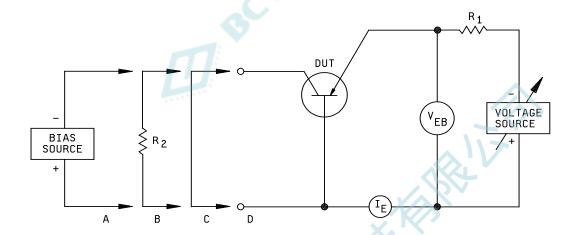

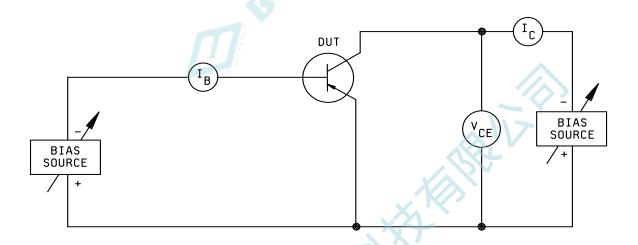

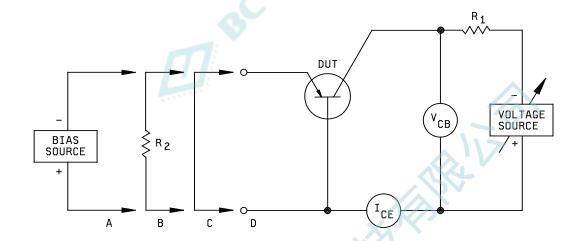

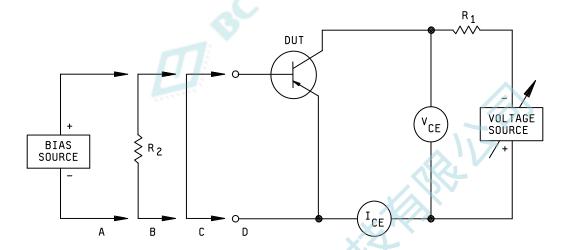

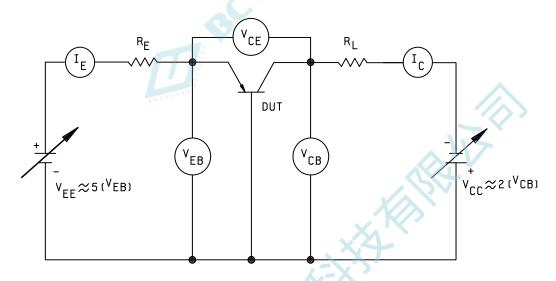

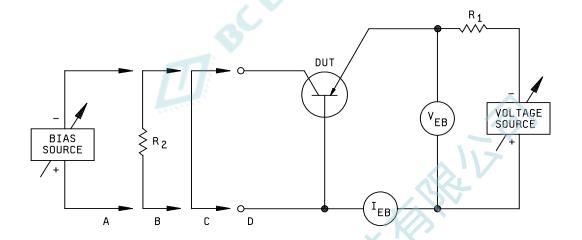

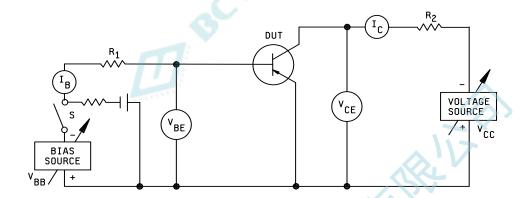

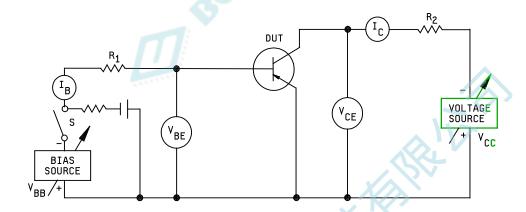

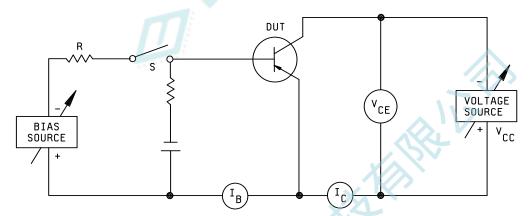

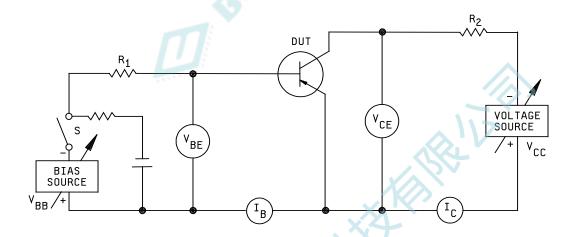

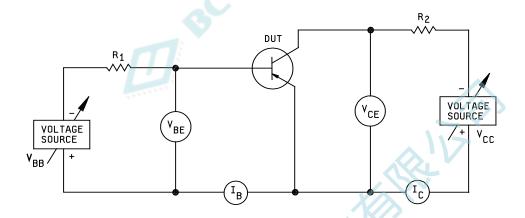

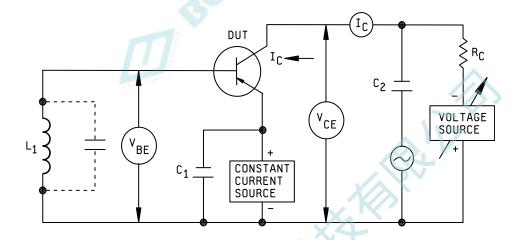

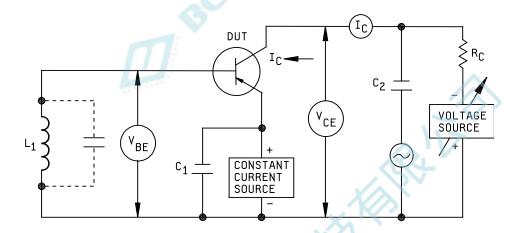

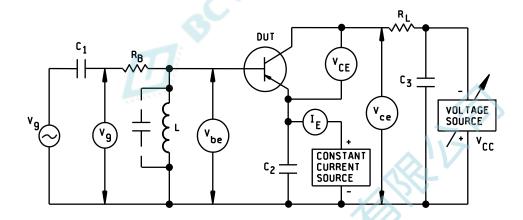

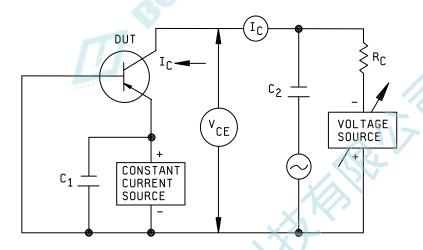

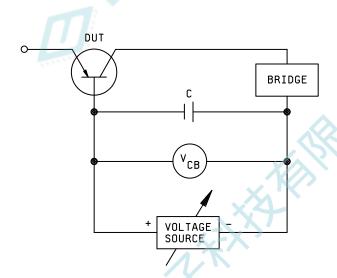

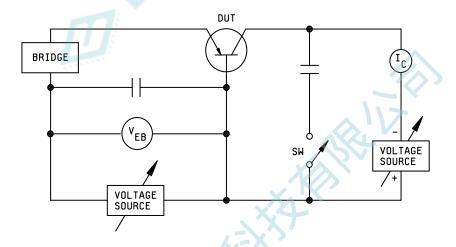

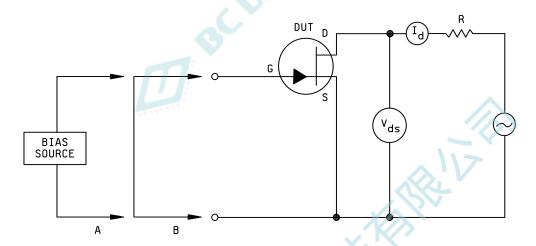

| Test circuit for breakdown voltage, collector to base  Test circuit for breakdown voltage, collector to emitter  Test circuit for floating potential  Test circuit for breakdown voltage, emitter to base  Test circuit for collector to emitter voltage  Test circuit for collector to emitter voltage  Test circuit for collector to base cutoff current  Test circuit for SOA (continuous dc)  Test circuit for SOA (pulsed)  Test circuit for SOA (switching)  Test circuit for base cutoff current  Test circuit for soa (switching)  Test circuit for soa (switching)  Test circuit for base emitter voltage (saturated or nonsaturated)  Test circuit for saturation voltage and resistance  Test circuit for static input resistance  Test circuit for static input resistance  Test circuit for static transconductance |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

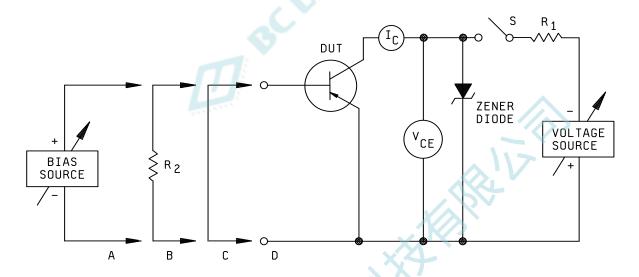

| Test circuit for breakdown voltage, collector to emitter  Test circuit for floating potential  Test circuit for breakdown voltage, emitter to base  Test circuit for collector to emitter voltage  Test circuit for collector to base cutoff current  Test circuit for collector to emitter cutoff current  Test circuit for collector to emitter cutoff current  Test circuit for SOA (continuous dc)  Test circuit for SOA (pulsed)  Test circuit for SOA (switching)  Test circuit for emitter to base cutoff current  Test circuit for base emitter voltage (saturated or nonsaturated)  Test circuit for saturation voltage and resistance  Test circuit for forward current transfer ratio  Test circuit for static input resistance                                                                                       |

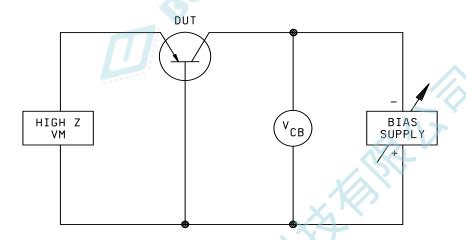

| Test circuit for floating potential  Test circuit for breakdown voltage, emitter to base  Test circuit for collector to emitter voltage  Test circuit for collector to base cutoff current  Test circuit for collector to emitter cutoff current  Test circuit for collector to emitter cutoff current  Test circuit for SOA (continuous dc)  Test circuit for SOA (pulsed)  Test circuit for SOA (switching)  Test circuit for emitter to base cutoff current  Test circuit for emitter to base cutoff current  Test circuit for base emitter voltage (saturated or nonsaturated)  Test circuit for saturation voltage and resistance  Test circuit for forward current transfer ratio  Test circuit for static input resistance                                                                                                |

| 3030–1 Test circuit for collector to emitter voltage 3036–1 Test circuit for collector to base cutoff current 3041–1 Test circuit for collector to emitter cutoff current 3051–1 Test circuit for SOA (continuous dc) 3052–1 Test circuit for SOA (pulsed) 3053–1 Test circuit for SOA (switching) 3061–1 Test circuit for emitter to base cutoff current 3066–1 Test circuit for base emitter voltage (saturated or nonsaturated) 3071–1 Test circuit for saturation voltage and resistance 3076–1 Test circuit for forward current transfer ratio 3086–1 Test circuit for static input resistance                                                                                                                                                                                                                              |

| Test circuit for collector to base cutoff current  3041–1 Test circuit for collector to emitter cutoff current  3051–1 Test circuit for SOA (continuous dc)  3052–1 Test circuit for SOA (pulsed)  3053–1 Test circuit for SOA (switching)  3061–1 Test circuit for emitter to base cutoff current  3066–1 Test circuit for base emitter voltage (saturated or nonsaturated)  3071–1 Test circuit for saturation voltage and resistance  3076–1 Test circuit for forward current transfer ratio  3086–1 Test circuit for static input resistance                                                                                                                                                                                                                                                                                 |

| Test circuit for collector to emitter cutoff current  Test circuit for SOA (continuous dc)  Test circuit for SOA (pulsed)  Test circuit for SOA (switching)  Test circuit for emitter to base cutoff current  Test circuit for base emitter voltage (saturated or nonsaturated)  Test circuit for saturation voltage and resistance  Test circuit for forward current transfer ratio  Test circuit for static input resistance                                                                                                                                                                                                                                                                                                                                                                                                   |

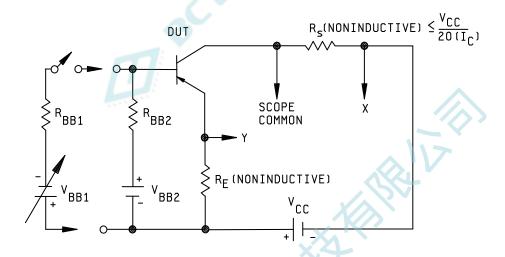

| 3051–1 Test circuit for SOA (continuous dc) 3052–1 Test circuit for SOA (pulsed) 3053–1 Test circuit for SOA (switching) 3061–1 Test circuit for emitter to base cutoff current 3066–1 Test circuit for base emitter voltage (saturated or nonsaturated) 3071–1 Test circuit for saturation voltage and resistance 3076–1 Test circuit for forward current transfer ratio 3086–1 Test circuit for static input resistance                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3052–1 Test circuit for SOA (pulsed) 3053–1 Test circuit for SOA (switching) 3061–1 Test circuit for emitter to base cutoff current 3066–1 Test circuit for base emitter voltage (saturated or nonsaturated) 3071–1 Test circuit for saturation voltage and resistance 3076–1 Test circuit for forward current transfer ratio 3086–1 Test circuit for static input resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

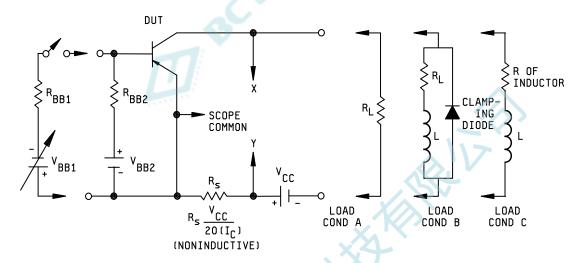

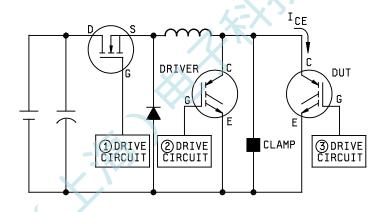

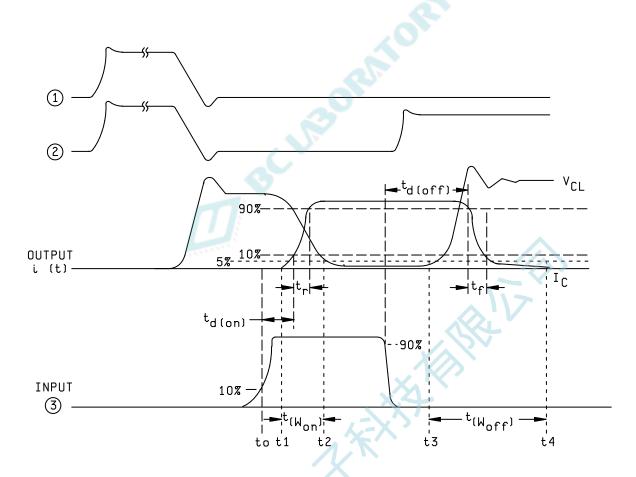

| 3053–1 Test circuit for SOA (switching) 3061–1 Test circuit for emitter to base cutoff current 3066–1 Test circuit for base emitter voltage (saturated or nonsaturated) 3071–1 Test circuit for saturation voltage and resistance 3076–1 Test circuit for forward current transfer ratio 3086–1 Test circuit for static input resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3061–1 Test circuit for emitter to base cutoff current 3066–1 Test circuit for base emitter voltage (saturated or nonsaturated) 3071–1 Test circuit for saturation voltage and resistance 3076–1 Test circuit for forward current transfer ratio 3086–1 Test circuit for static input resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3066–1 Test circuit for base emitter voltage (saturated or nonsaturated) 3071–1 Test circuit for saturation voltage and resistance 3076–1 Test circuit for forward current transfer ratio 3086–1 Test circuit for static input resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3071–1 Test circuit for saturation voltage and resistance 3076–1 Test circuit for forward current transfer ratio 3086–1 Test circuit for static input resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3076–1 Test circuit for forward current transfer ratio 3086–1 Test circuit for static input resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3086–1 Test circuit for static input resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

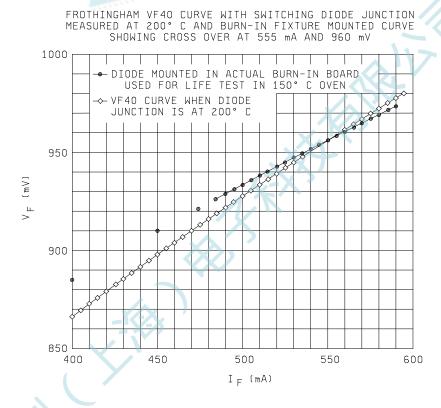

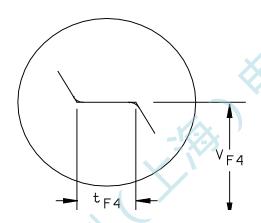

| 3100–1 Frothingham VF40 curve                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

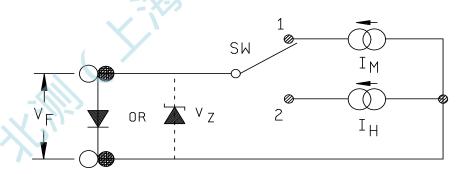

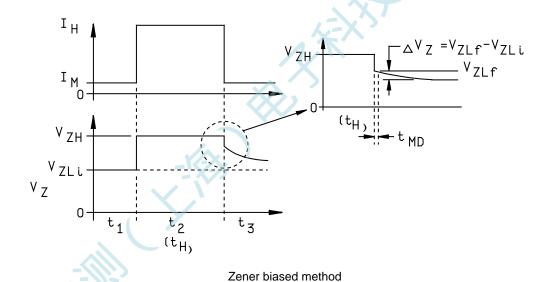

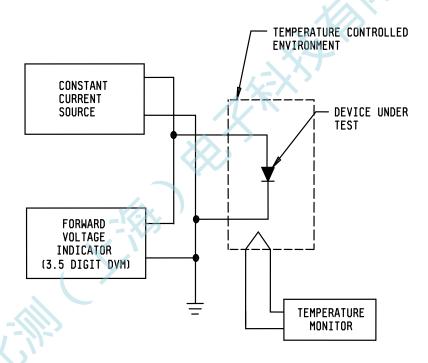

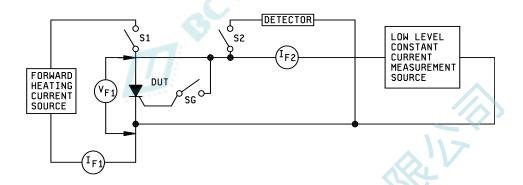

| 3101–1 Thermal impedance testing setup for diodes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

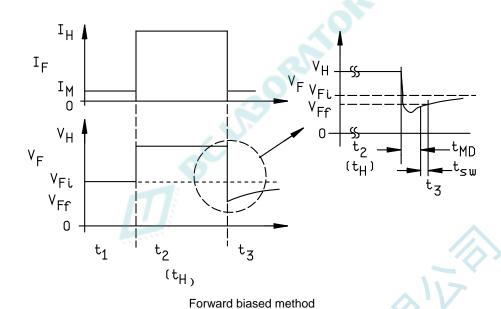

| 3101–2 Thermal impedance testing waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3101–3 Thermal impedance testing waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

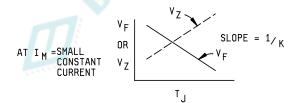

| 3101–4 Example curve of VF versus TJ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

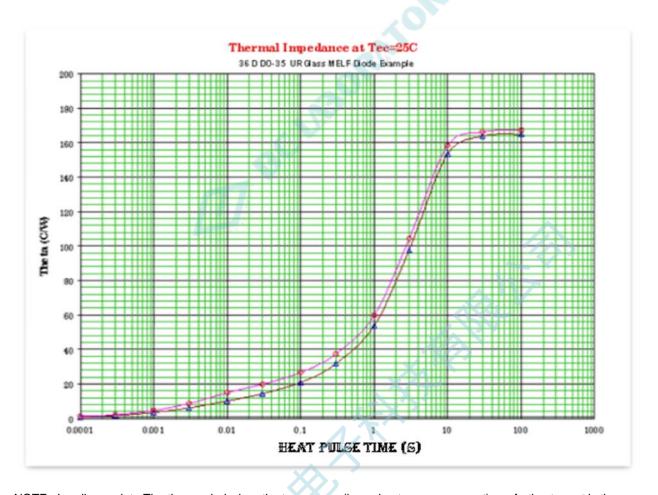

| 3101–5 Heating curves for two extreme devices (log-linear)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

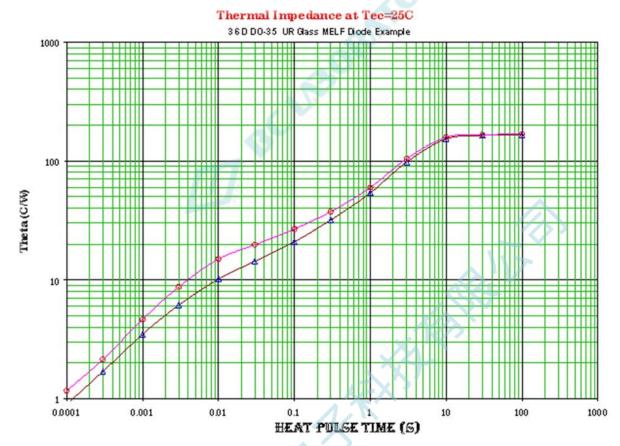

| 3101–6 Heating curves for two extreme devices (log-log)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

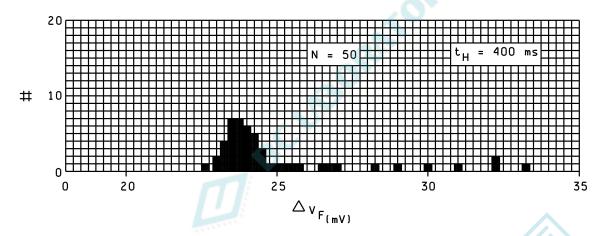

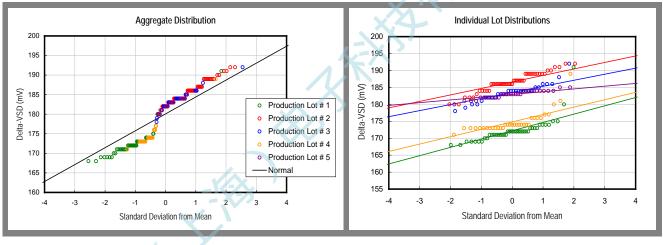

| 3101–7 Typical $\Delta V_F$ (or $Z_{\theta JX}$ ) distribution with asymmetrical histogram distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

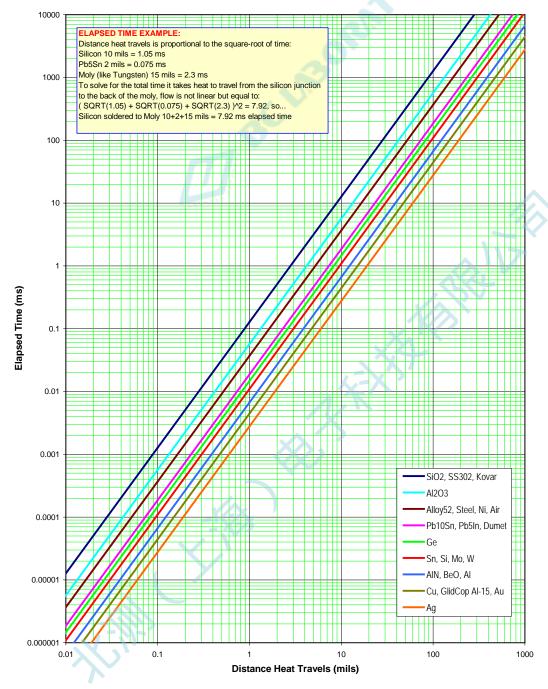

| 3101–A1 Heat flow distance vs. elapsed time plot                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

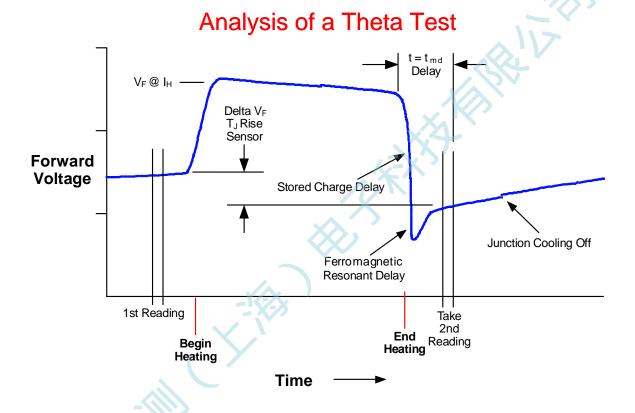

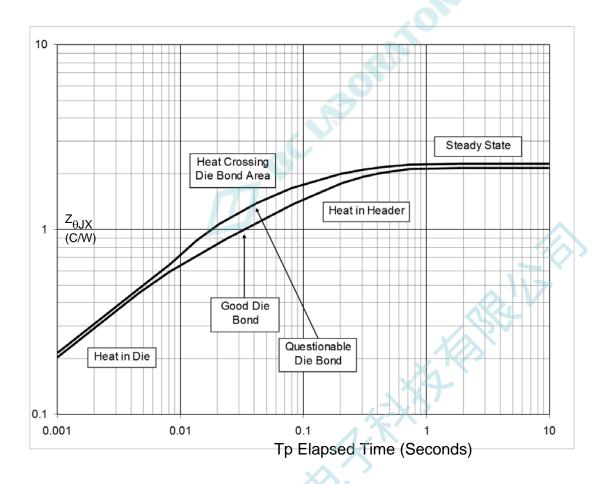

| 3101–B1 Analysis of theta test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

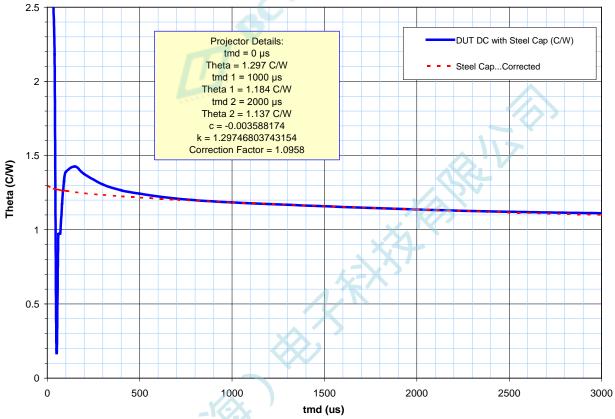

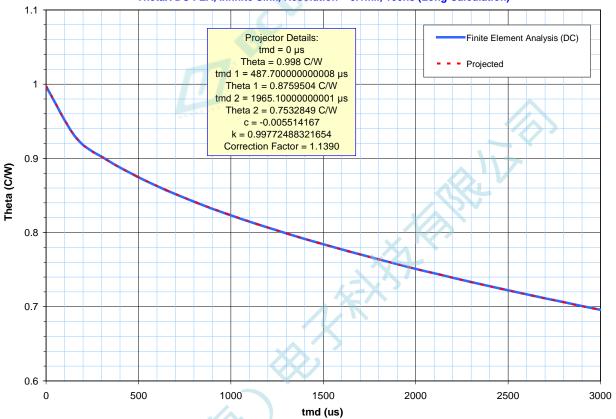

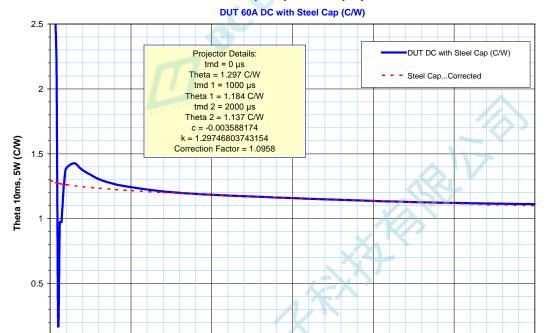

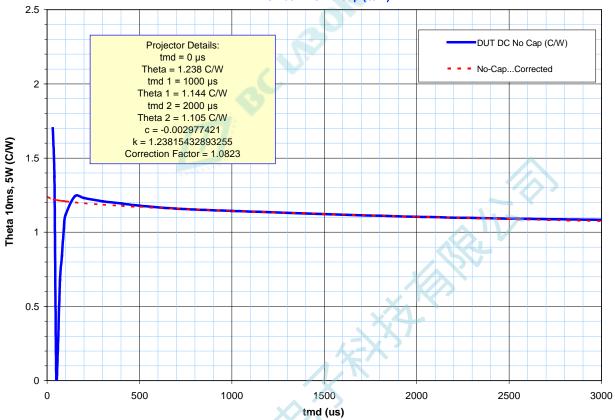

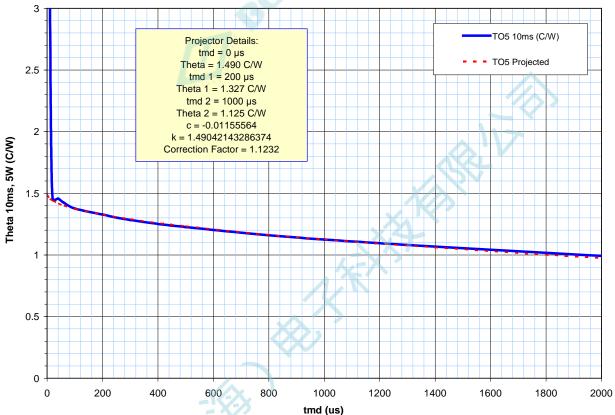

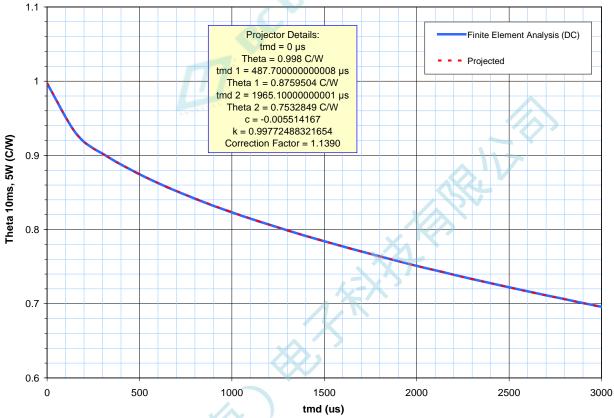

| 3101–B2 Theta versus t <sub>md</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

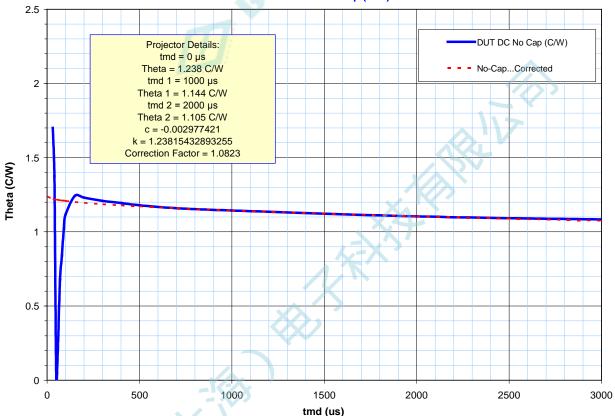

| 3101–B3 Theta versus t <sub>md</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

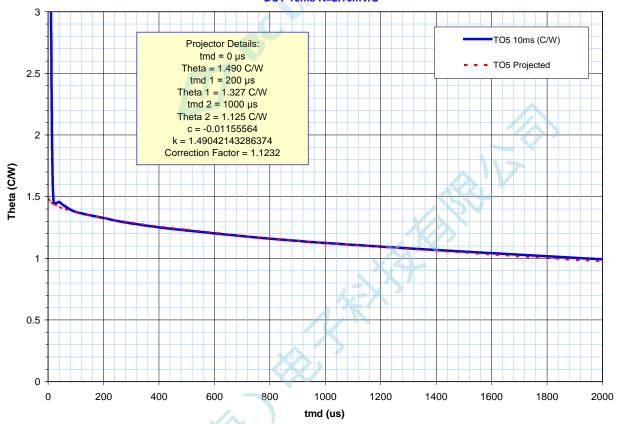

| 3101–B4 Theta versus t <sub>md</sub> 3101–B5 Theta versus t <sub>md</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

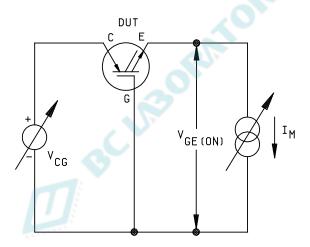

| 3103–1 K factor calibration setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

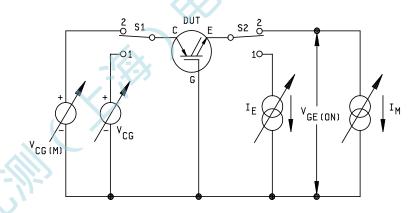

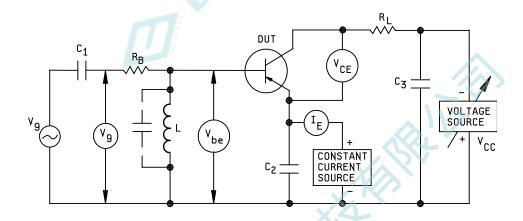

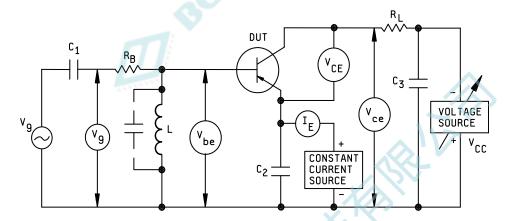

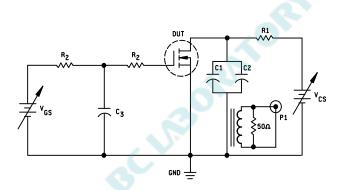

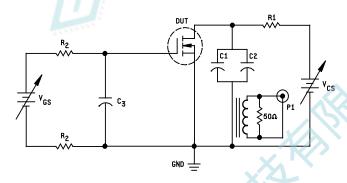

| 3103–2 Common gate thermal impedance measurement circuit (gate emitter on voltage method)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

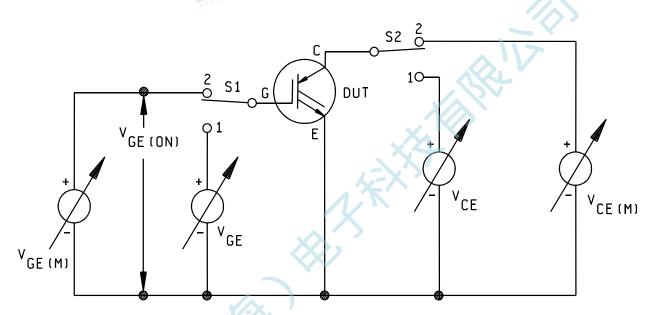

| 3103–3 Common source thermal impedance measurement circuit (gate emitter on voltage method)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

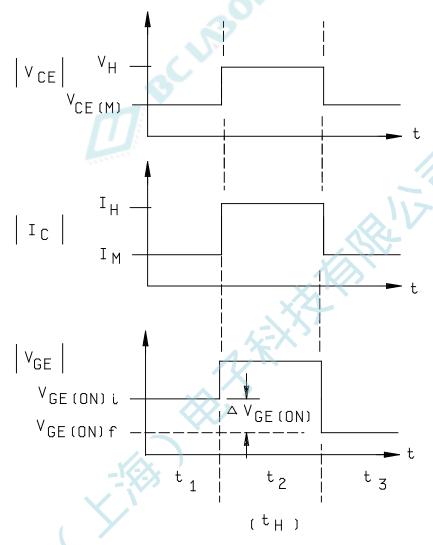

| 3103–4 Device waveforms during the three segments of the thermal transient test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

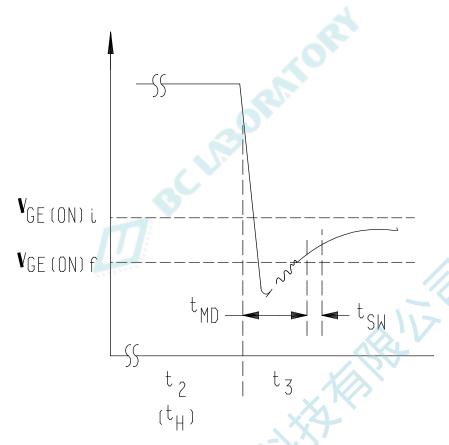

| 3103–5 Second V <sub>GE</sub> measurement waveform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

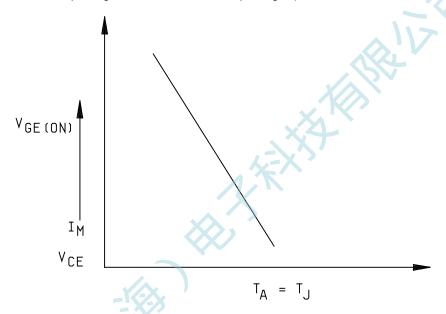

| 3103–6 Example curve of V <sub>GE(ON)</sub> versus T <sub>J</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

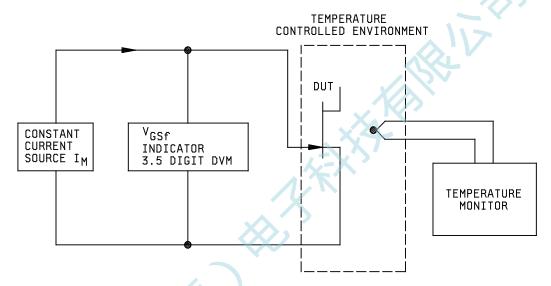

| 3104–1 K factor calibration setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

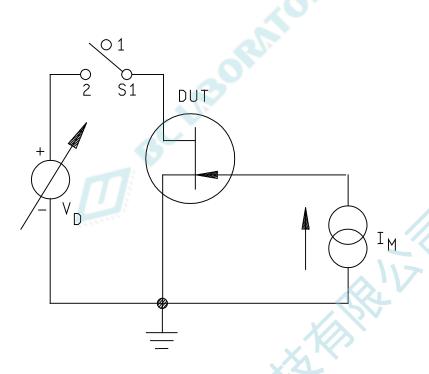

| 3104–2 Thermal resistance measurement circuit (constant current forward-biased gate voltage method)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

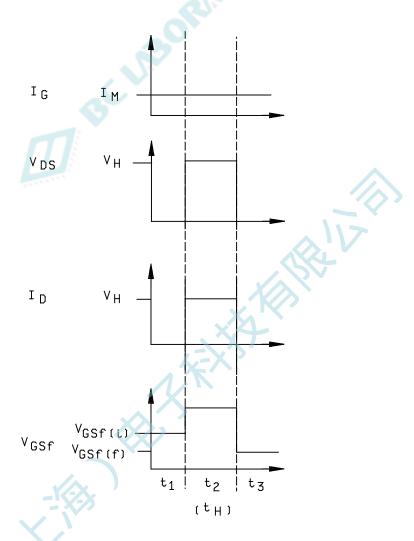

| 3104–3 Device waveforms during the three segments of the thermal resistance test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

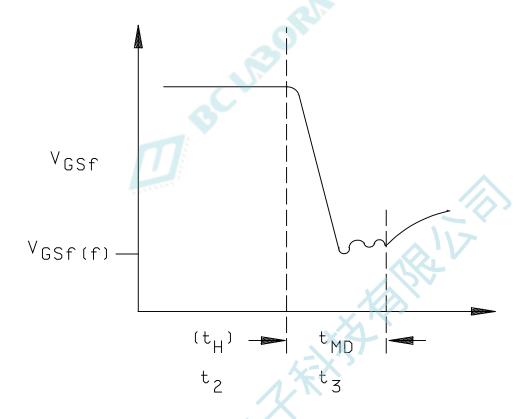

| 3104–4 Second V <sub>GSf</sub> measurement waveform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

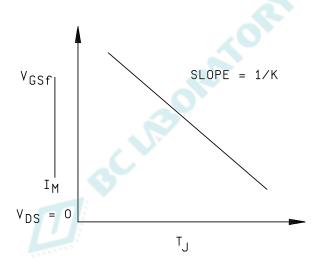

| 3104–5 Calibration curve                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

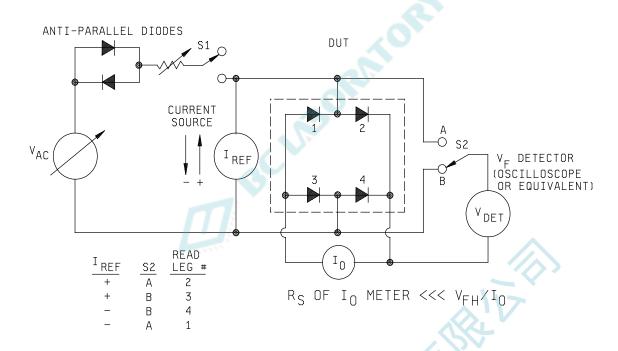

| 3105–1 Single-phase bridge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

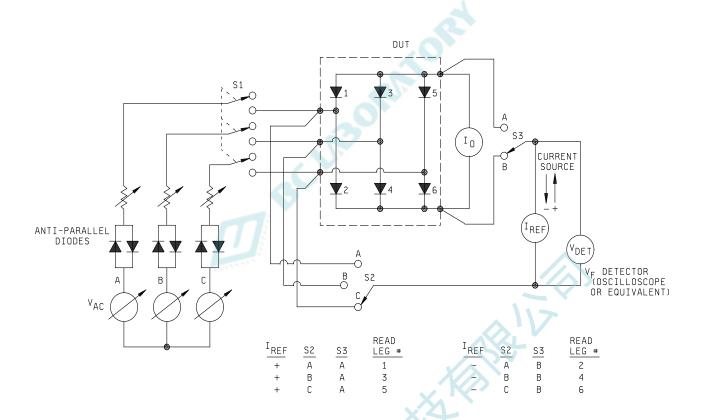

| 3105–2 Three-phase bridge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3105–3 Oscilloscope displays                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

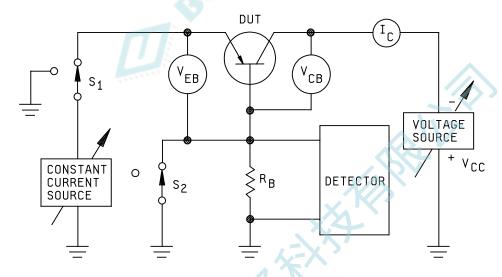

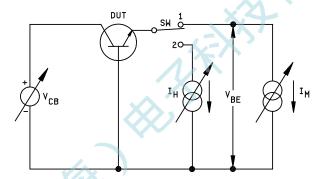

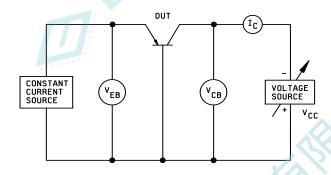

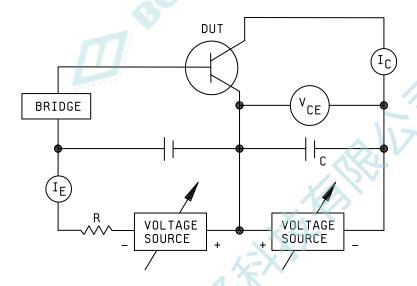

| 3126–1 Test circuit for thermal resistance (collector cutoff current method)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

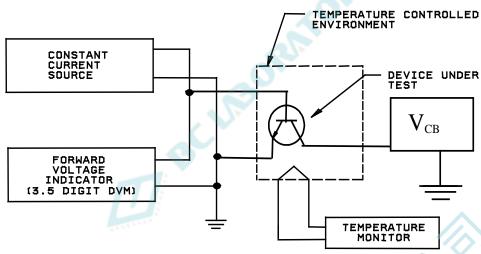

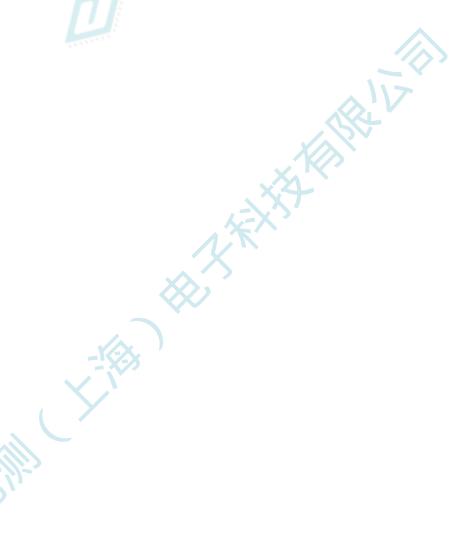

| 3131–1 Thermal impedance testing setup for transistors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

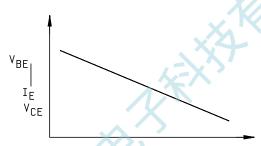

| 3131–2 Example curve of V <sub>BE</sub> versus T <sub>J</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

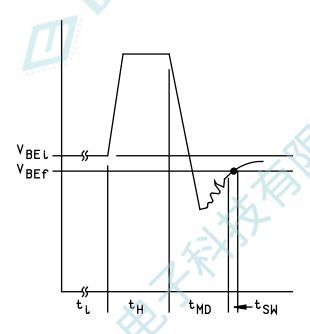

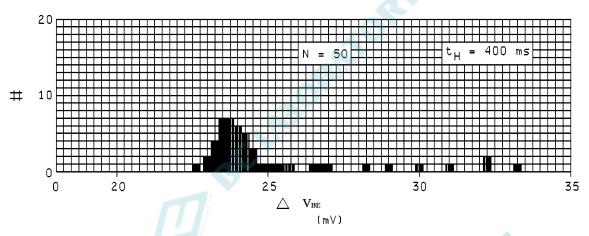

| 3131–3 Thermal impedance testing waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3131–4 Heating curves for two extreme devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

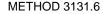

| 3131–5 Typical ∆V <sub>BE</sub> distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| <u>FIGURE</u> | <u>TITLE</u>                                                                                   |

|---------------|------------------------------------------------------------------------------------------------|

|               |                                                                                                |

| 3131–A1       | Analysis of a theta test                                                                       |

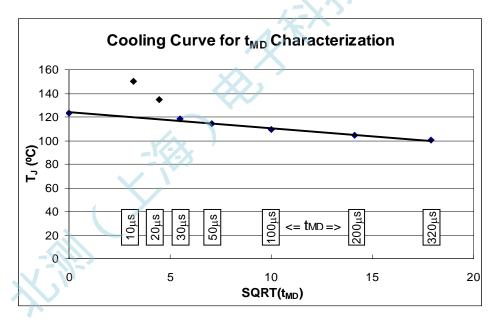

| 3131-A2       | Theta vs. t <sub>MD</sub>                                                                      |

| 3131–A3       | Theta vs. t <sub>MD</sub>                                                                      |

| 3131-A4       | Theta vs. t <sub>MD</sub>                                                                      |

| 3131-A5       | Theta vs. t <sub>MD</sub>                                                                      |

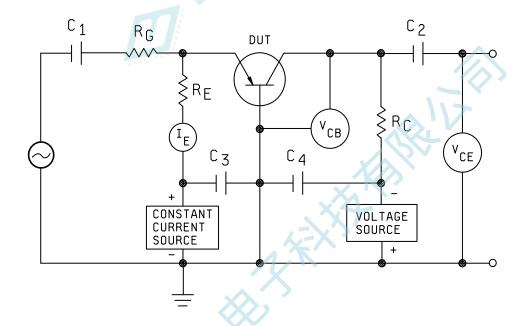

| 3132-1        | Test circuit for thermal resistance (dc forward voltage drop, emitter base, continuous method) |

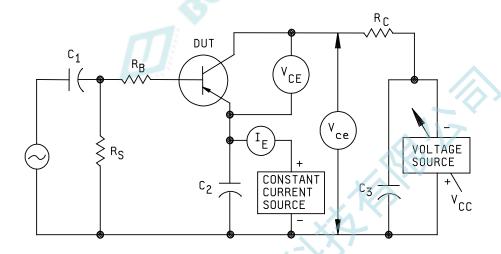

| 3136-1        | Test circuit for thermal resistance (forward voltage drop, collector to base, diode method)    |

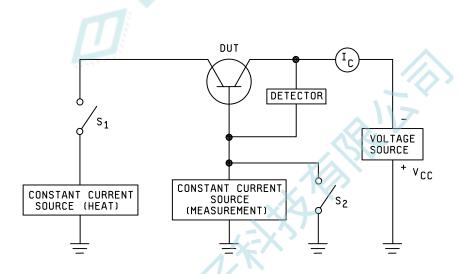

| 3161–1        | K-factor calibration setup                                                                     |

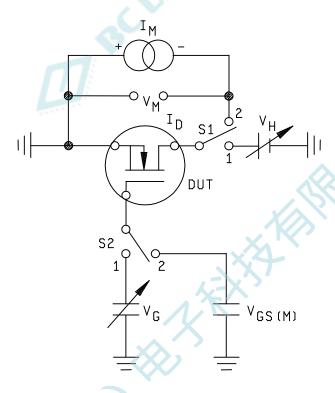

| 3161–2        | Thermal impedance measurement circuit (source drain diode method)                              |

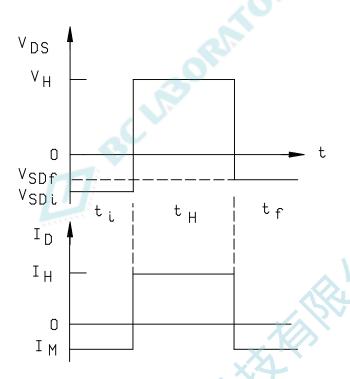

| 3161–3        | Device waveforms during the three segments of the thermal transient test                       |

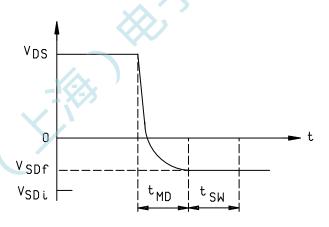

| 3161–4        | Second V <sub>SD</sub> ,measurement waveform                                                   |

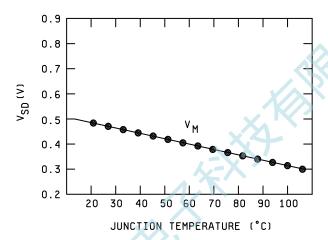

| 3161–5        | Example curve of V <sub>SD</sub> bversus T <sub>J</sub>                                        |

| 3131–6        | Cooling curve                                                                                  |

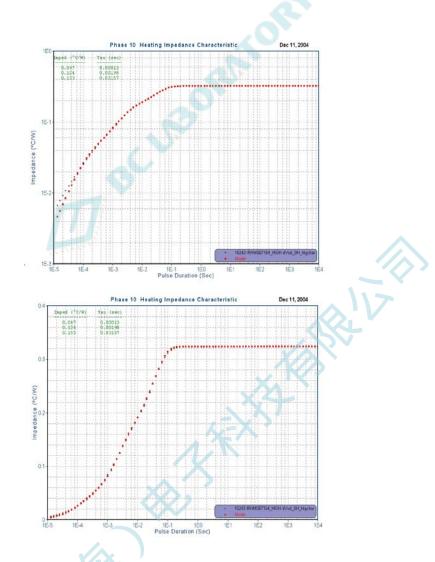

| 3161–7        | Heating curve and thermal model example                                                        |

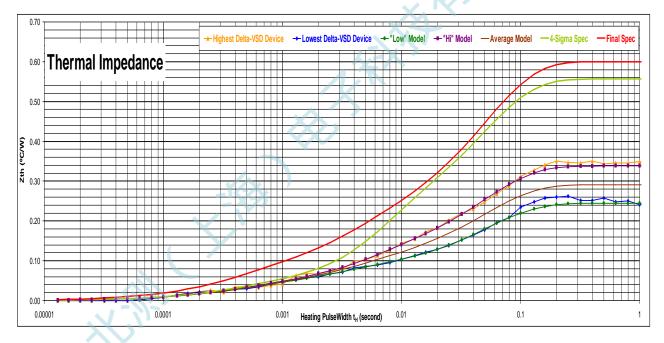

| 3161–8        | Thermal impedance curves                                                                       |

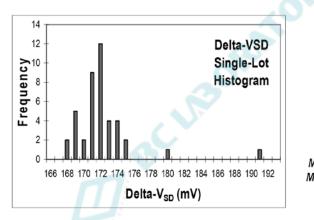

| 3161-9        | Delta VSD single lot histogram                                                                 |

| 3161-10       | Summary table and sample data from five production lots                                        |

| 3181-1        | Thermal resistance test circuit                                                                |

| 3201-1        | Test circuit for small-signal, short-circuit input impedance                                   |

| 3206-1        | Test circuit for small-signal, short-circuit forward-current transfer ratio                    |

| 3211-1        | Test circuit for small-signal, open-circuit reverse-voltage transfer ratio                     |

| 3216-1        | Test circuit for small-signal, open-circuit output admittance                                  |

| 3221-1        | Test circuit for small-signal, short-circuit input admittance                                  |

| 3231-1        | Test circuit for small-signal short-circuit output admittance                                  |

| 3236-1        | Test circuit for open-circuit output capacitance                                               |

| 3240-1        | Test circuit for input capacitance (output open-circuited or short-circuited)                  |

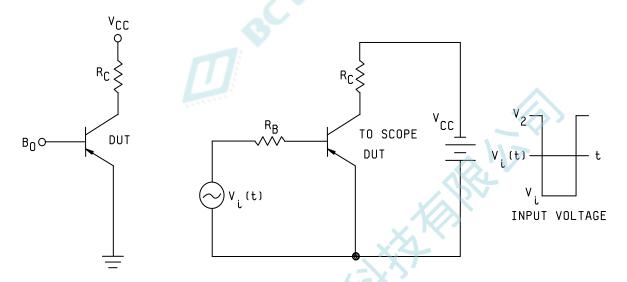

| 3251-1        | Test circuit for pulse response, test condition A                                              |

| 3251-2        | Test circuit for pulse response, test condition B                                              |

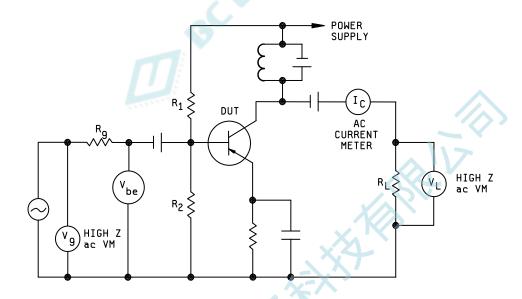

| 3256-1        | Test circuit for small-signal power gain                                                       |

| 3266-1        | Test circuit for real part of small-signal short-circuit input impedance                       |

| 3301-1        | Test circuit for small-signal, short-circuit forward-current transfer ratio cutoff frequency   |

| 3306-1        | Test circuit for small-signal, short-circuit forward-current transfer ratio                    |

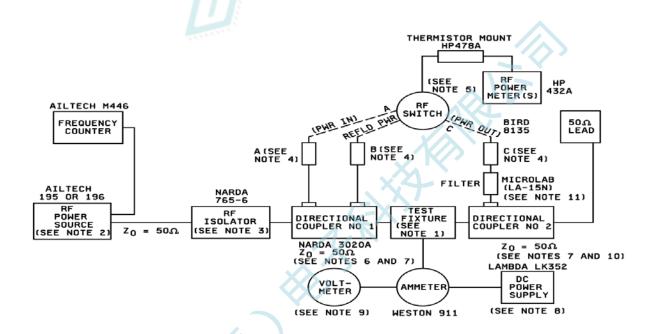

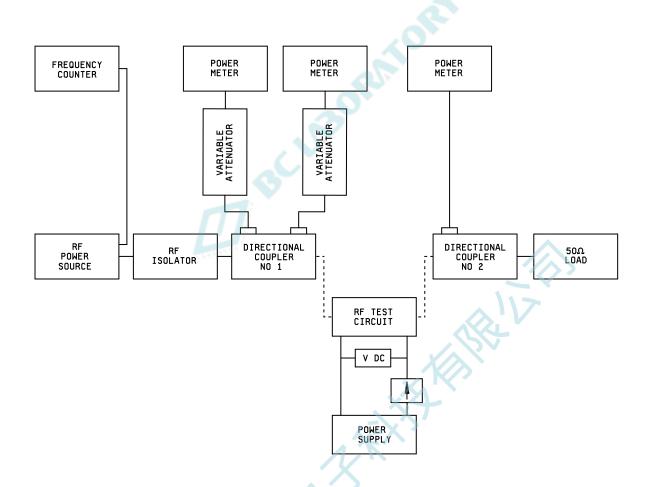

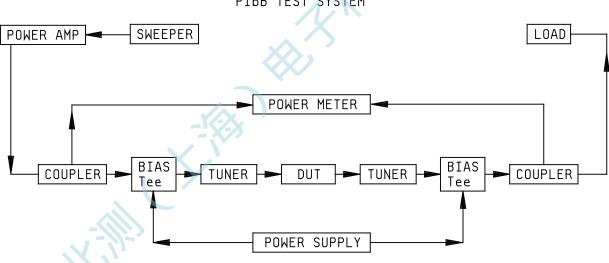

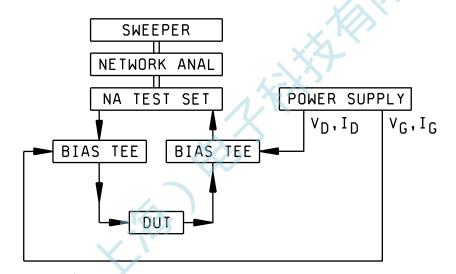

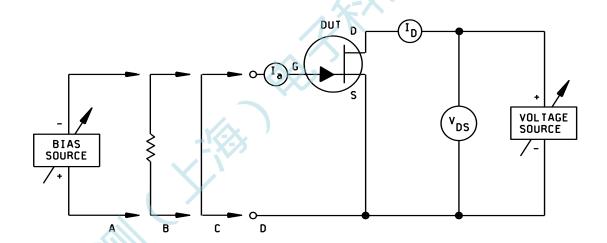

| 3320-1        | Test equipment setup                                                                           |

| 3320-2        | Alternate test equipment setup                                                                 |

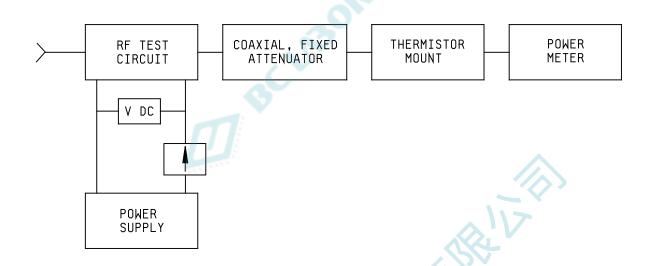

| 3320-3        | RF test setup                                                                                  |

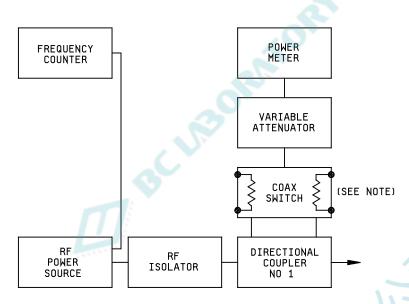

| 3320-4        | Alternate output setup                                                                         |

| 3320-5        | Alternate input setup                                                                          |

| 3401-1        | Test circuit for breakdown voltage, gate-to-source                                             |

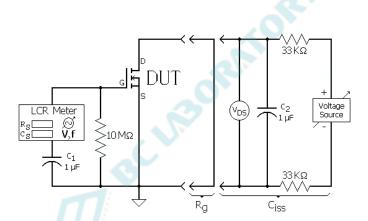

| 3402-1        | Gate ESR testing setup for MOSFETs – Condition B                                               |

| 3402-2        | Gate ESR testing setup for MOSFETs – Condition A                                               |

| 3403-1        | Test circuit for breakdown voltage, gate-to-source                                             |

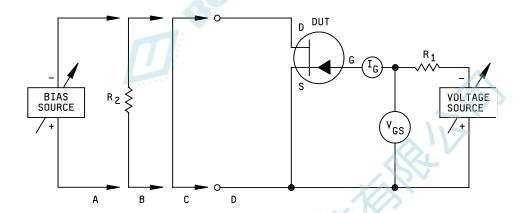

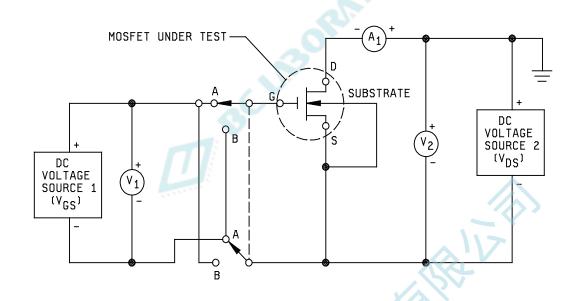

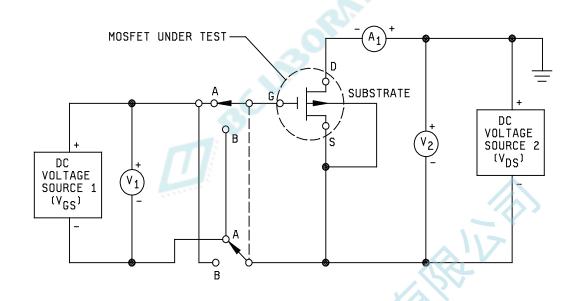

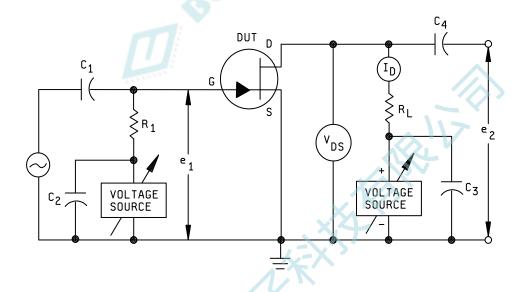

| 3404-1        | Test circuit for n-channel MOSFETs                                                             |

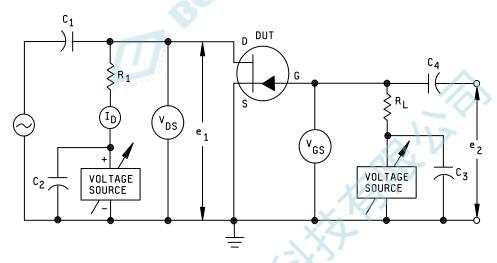

| 3404-2        | Test circuit for p-channel MOSFETS                                                             |

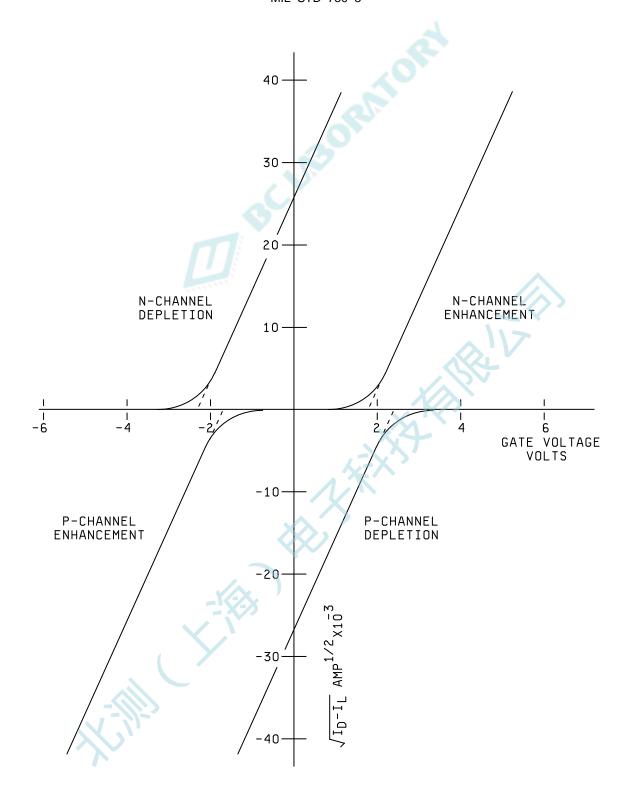

| 3404-3        | Examples of curves                                                                             |

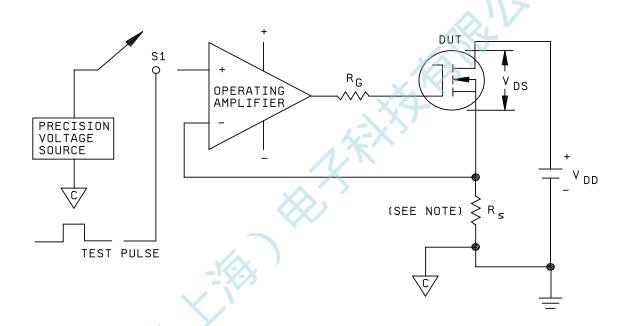

| 3405-1        | Test circuit for drain-to-source on-state voltage                                              |

| 3407–1        | Test circuit for breakdown voltage, drain-to-source                                            |

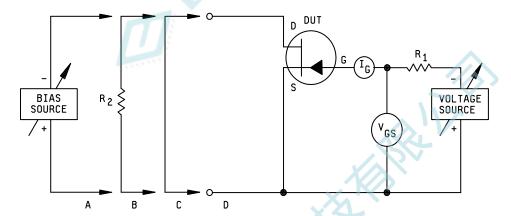

| 3411–1        | Test circuit for gate reverse current                                                          |

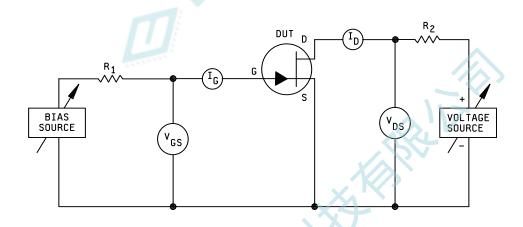

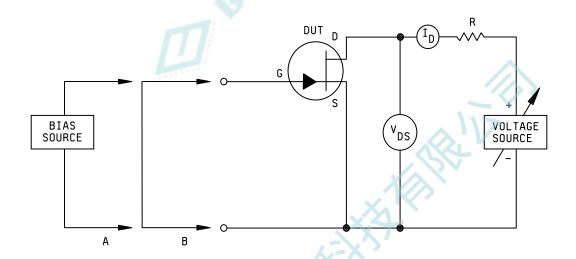

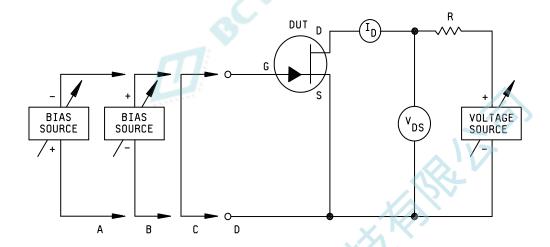

| 3413–1        | Test circuit for drain current                                                                 |

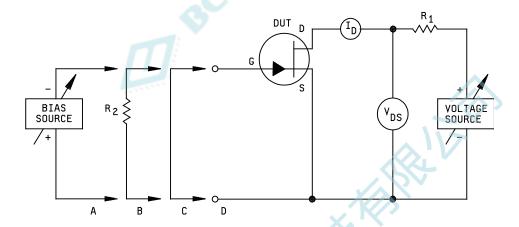

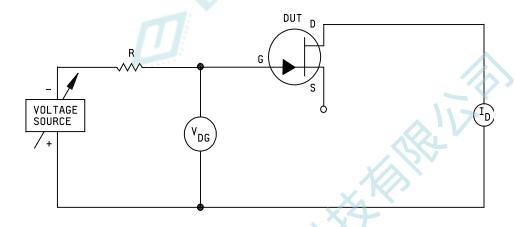

| 3415-1        | Test circuit for reverse drain current                                                         |

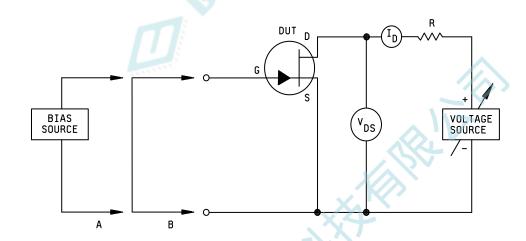

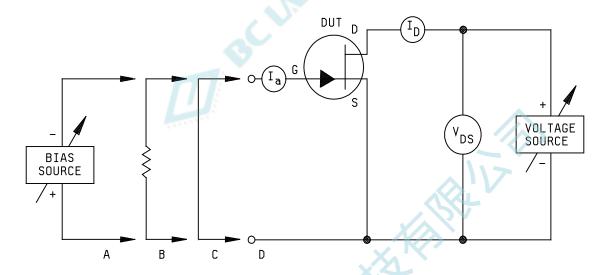

| 3421-1        | Test circuit for static drain-to-source on-state resistance                                    |

| 3423-1        | Test circuit for small-signal, drain-to-source on-state resistance                             |

| <u>FIGURE</u>    | TITLE AND THE STATE OF THE STAT |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

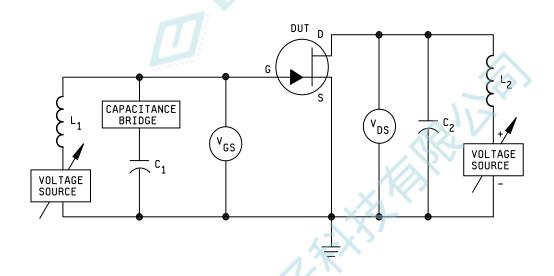

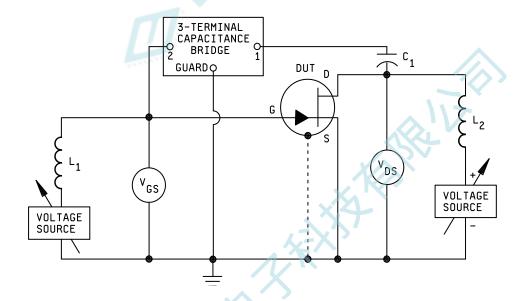

| 3431-1           | Test circuit for small-signal, common-source, short-circuit, input capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3433-1           | Test circuit for small-signal, common-source, short-circuit, reverse transfer capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3453-1           | Test circuit for small-signal, common-source, short-circuit, output admittance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

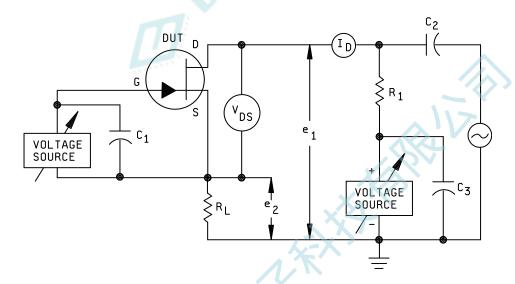

| 3455-1           | Test circuit for small-signal, common-source, short-circuit, forward admittance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3457-1           | Test circuit for small-signal, common-source, short-circuit, reverse transfer admittance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

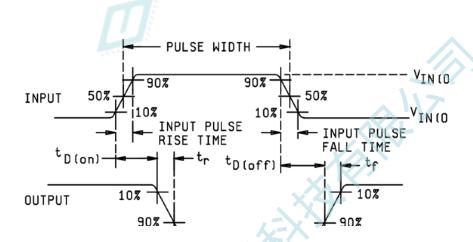

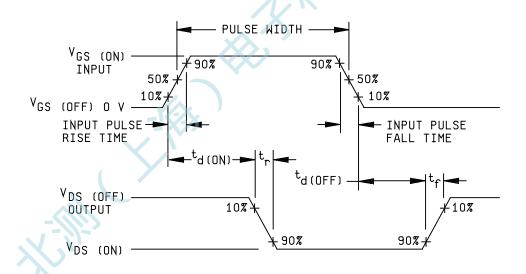

| 3459-1           | Pulse characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3461-1           | Test circuit for small-signal, common-source, short-circuit, input admittance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

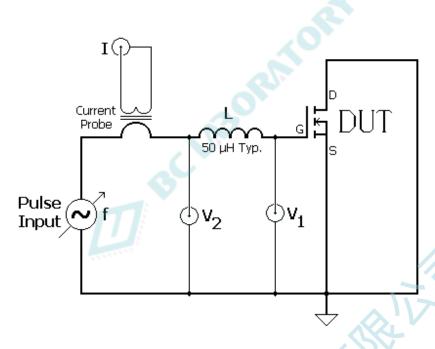

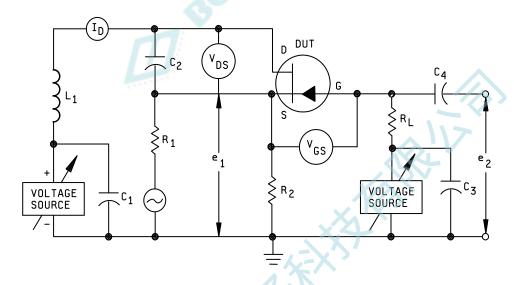

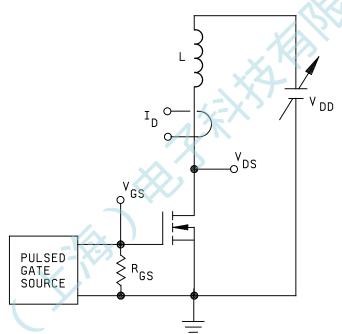

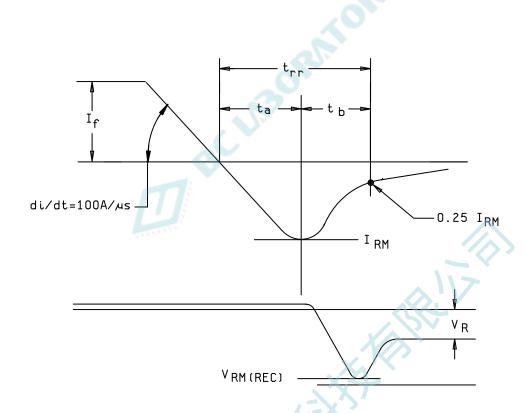

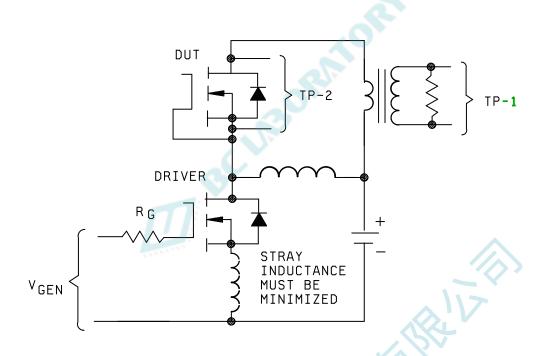

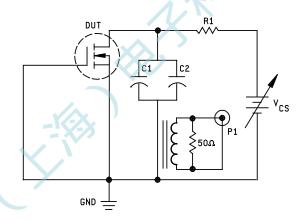

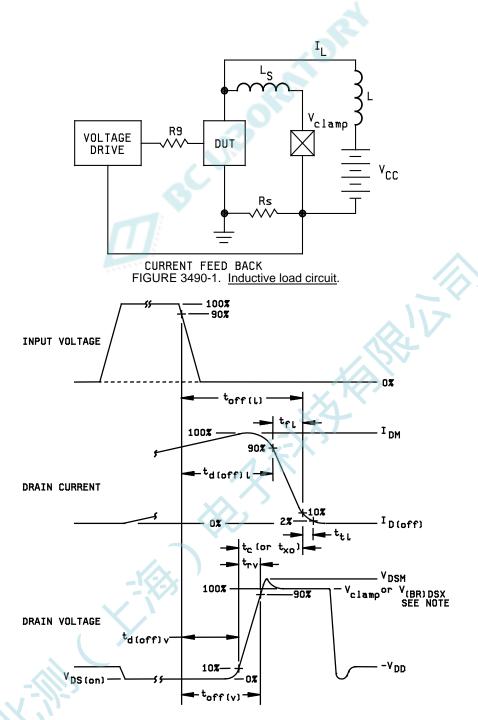

| 3470–1           | Unclamped inductive switching circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

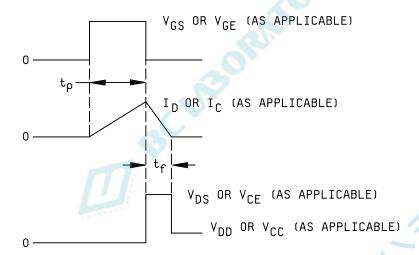

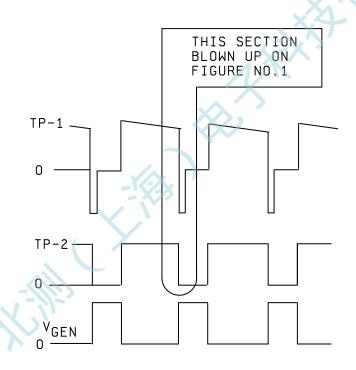

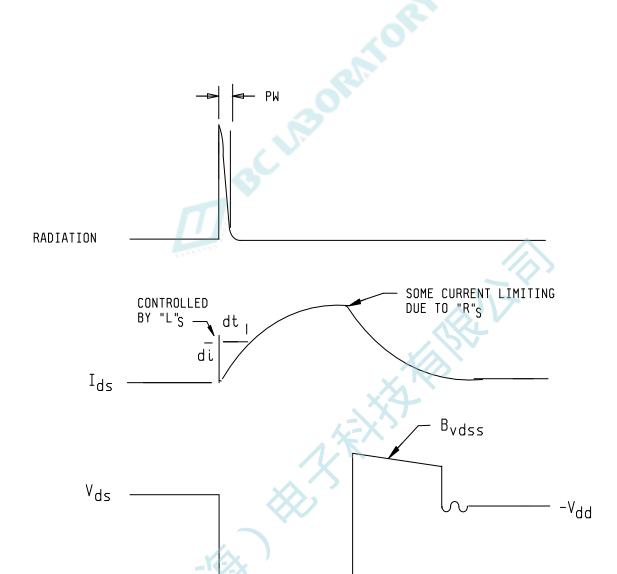

| 3470–2           | Unclamped inductive switching power pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

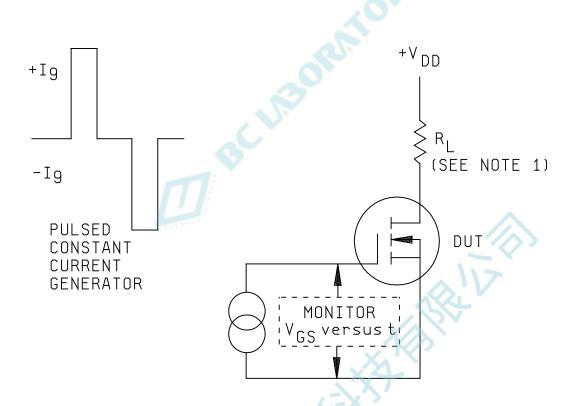

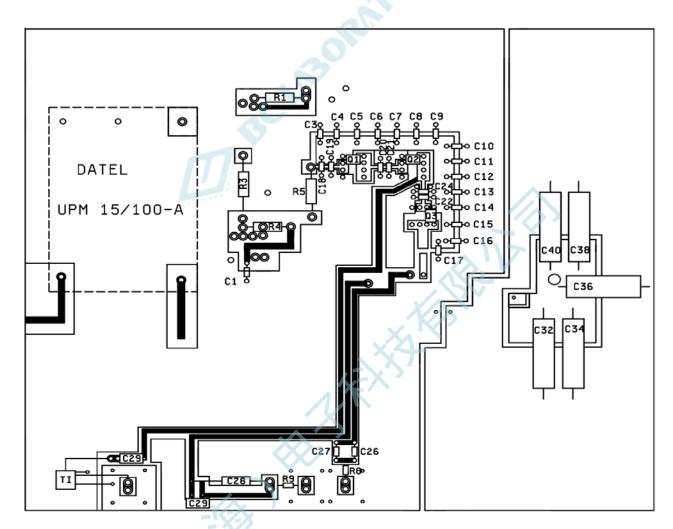

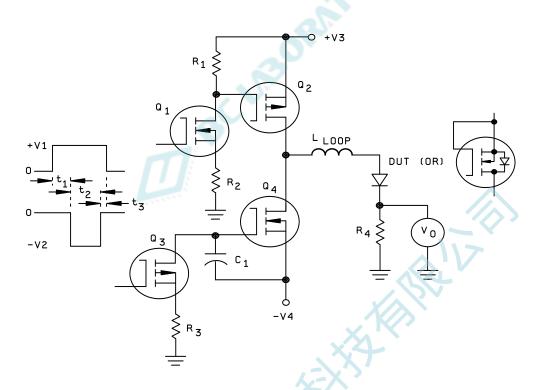

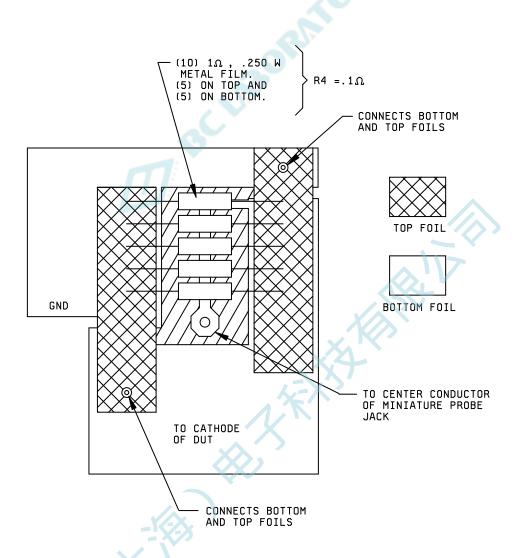

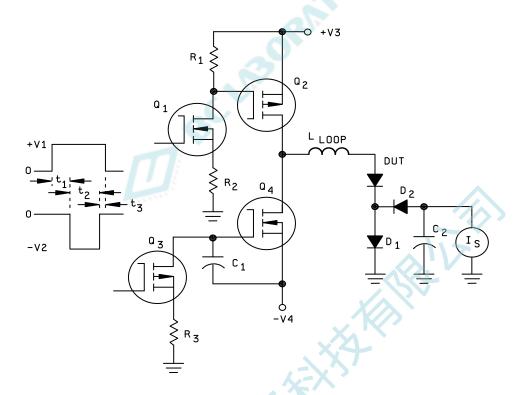

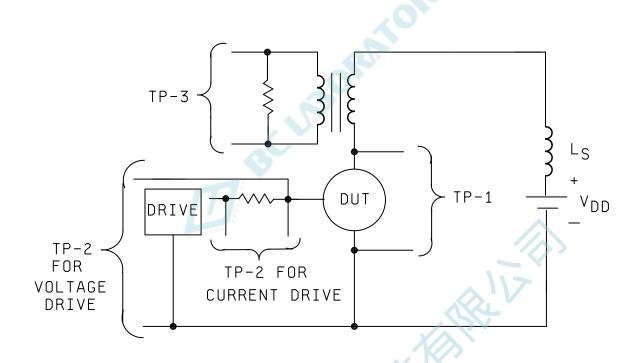

| 3471–1           | Pulsed constant current generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

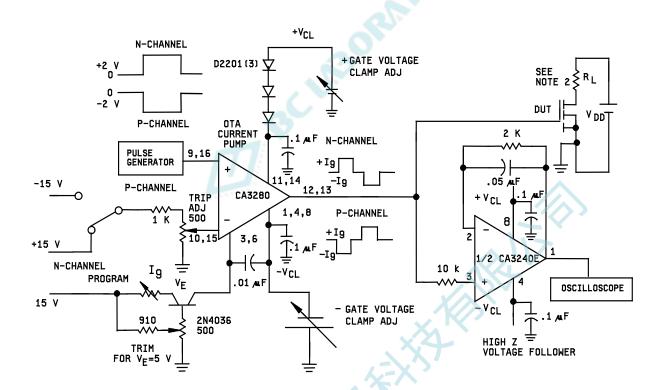

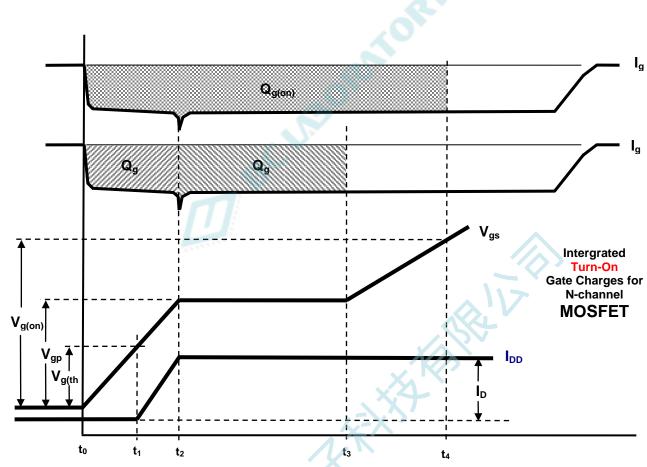

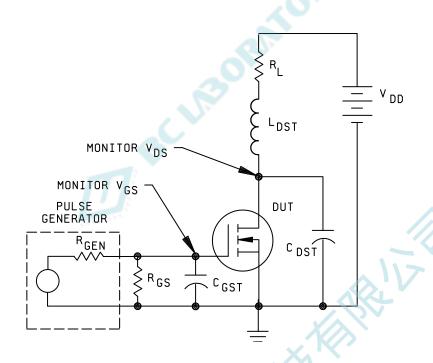

| 3471–2           | Practical gate charge test circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

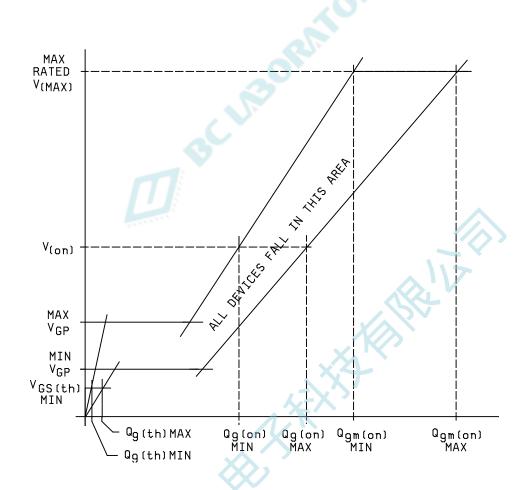

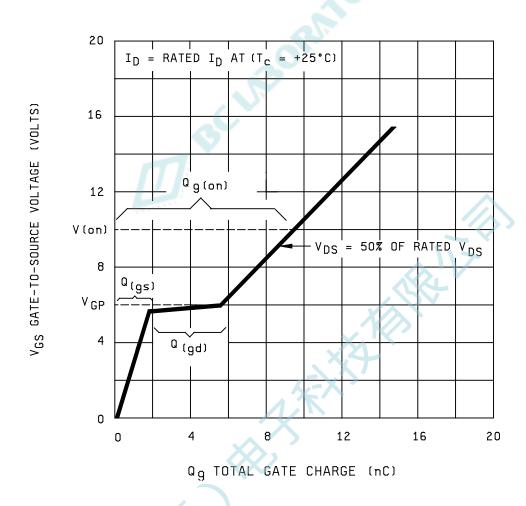

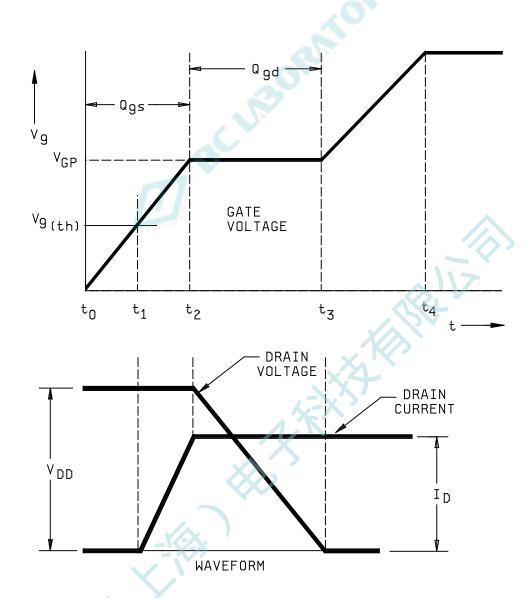

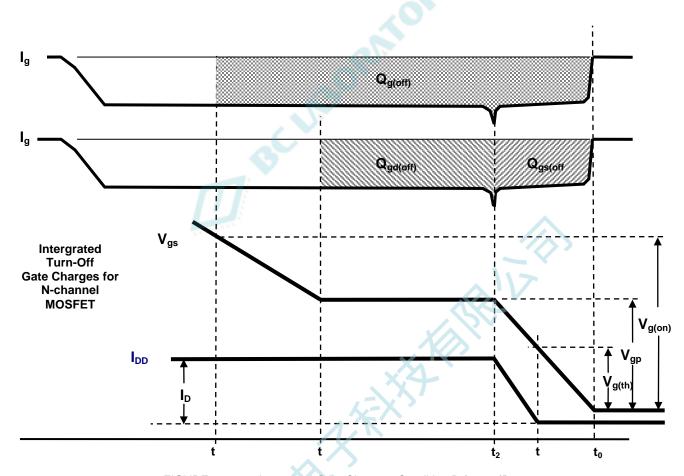

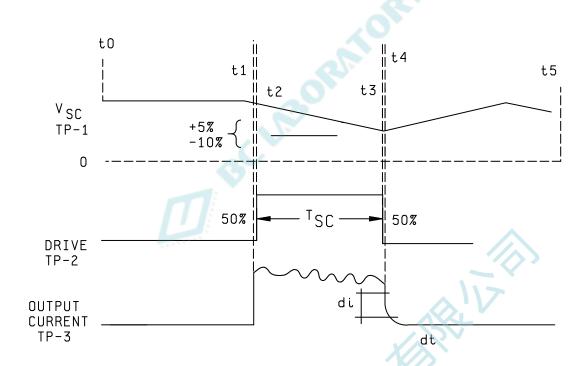

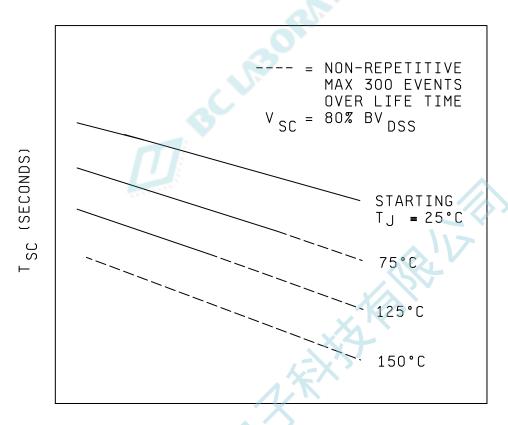

| 3471–3           | Gate charge characterization showing measured characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |