# JEDEC STANDARD

# **Temperature Cycling**

**JESD22-A104E**

(Revision of JESD22-A104D, March 2009)

OCTOBER 2014

JEDEC SOLID STATE TECHNOLOGY ASSOCIATION

联系方式:xuyj@beice-sh.com 1391716567

#### NOTICE

JEDEC standards and publications contain material that has been prepared, reviewed, and approved through the JEDEC Board of Directors level and subsequently reviewed and approved by the JEDEC legal counsel.

JEDEC standards and publications are designed to serve the public interest through eliminating misunderstandings between manufacturers and purchasers, facilitating interchangeability and improvement of products, and assisting the purchaser in selecting and obtaining with minimum delay the proper product for use by those other than JEDEC members, whether the standard is to be used either domestically or internationally.

JEDEC standards and publications are adopted without regard to whether or not their adoption may involve patents or articles, materials, or processes. By such action JEDEC does not assume any liability to any patent owner, nor does it assume any obligation whatever to parties adopting the JEDEC standards or publications.

The information included in JEDEC standards and publications represents a sound approach to product specification and application, principally from the solid state device manufacturer viewpoint. Within the JEDEC organization there are procedures whereby a JEDEC standard or publication may be further processed and ultimately become an ANSI standard.

No claims to be in conformance with this standard may be made unless all requirements stated in the standard are met.

Inquiries, comments, and suggestions relative to the content of this JEDEC standard or publication should be addressed to JEDEC at the address below, or refer to <u>www.jedec.org</u> under Standards and Documents for alternative contact information.

> Published by ©JEDEC Solid State Technology Association 2014 3103 North 10th Street Suite 240 South Arlington, VA 22201-2107

This document may be downloaded free of charge; however JEDEC retains the copyright on this material. By downloading this file the individual agrees not to charge for or resell the resulting material.

#### **PRICE: Contact JEDEC**

Printed in the U.S.A. All rights reserved

联系方式:xuyj@beice-sh.com 1391716567

With Life and the second secon

#### TEST METHOD A104E TEMPERATURE CYCLING

(From Board Ballot JCB-00-16, JCB-05-82, JCB-09-20, and JCB-14-45, formulated under the cognizance of the JC-14.1 Committee on Reliability Test Methods for Packaged Devices.)

#### 1 Scope

This standard applies to single-, dual- and tr iple-chamber temperature cycling and covers component and solder interconnection testing. It should be noted that this standard does not cover or apply to thermal shock chambers. In single chamber cycling, the load is placed in a stationary chamber and is heated or cooled by introducing hot or co ld air into the cham ber. In dual-chamber cycling, the load is placed on a movi ng platform that shuttles between stationary chambers maintained at fixed tem peratures. In triple-chamber temperature cycling there are three chambers and the load is moved between them.

This test is conducted to determ ine the ability of components and so lder interconnects to withstand mechanical stresses induced by alternating high- and low -temperature extremes. Permanent changes in electrical and/or physical characteristics can result from these mechanical stresses.

# 2 Terms and definitions

**2.1** load: The sample(s) and associated fixtures (trays, racks, etc.) in the chamber during the test.

**2.2 working zone:** The volume in the cham ber(s) in which the temperature of the load is controlled within the specified conditions.

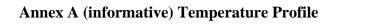

**2.3** sample temperature  $(T_s)$ : The temperature of the samples during temperature cycling, as measured by thermocouples or equivalent temperature measurement apparatus affixed to, or imbedded in, their bodies.

NOTE The thermocouple, or equivalent temperature measurement apparatus, attachment method used should ensure that the entire mass of the sam ple(s) is reaching the temperature extremes and the soak requirements.

**2.4 maximum sample temperature:**  $(T_{s(max)})$ : The maximum temperature experienced by the sample(s) as measured by thermocouples, per 3.3.

**2.5 minimum sample temperature:**  $(T_{s(min)})$ : The minimum temperature experienced by the sample(s) as measured by thermocouples, per 3.3.

# 2 Terms and definitions (cont'd)

**2.6 load transfer time:** The time it takes to physically transfer the load from one temperature chamber and introduce it into the othe r. Load transfer applie s to dual and triple chamber cycling.

**2.7 maximum load:** The largest lo ad that can be placed in the cham ber and still meet the specified temperature cycling requirements as verified by thermocouples, per 3.3.

**2.8** nominal  $\Delta T$ : The difference between nom inal  $T_{s(max)}$  and nom inal  $T_{s(min)}$  for the Temperature Cycling Test Condition; see Table 1.

**2.9** soak time: The total time the sample tem perature is within a specified range of each nominal  $T_{s(\text{max})}$  and nominal  $T_{s(\text{min})}$ . This range is defined as the time  $T_s$  is at -5 °C to +10 °C /+15 °C (dependent on the Te st Condition tolerance) of  $T_{s(\text{max})}$  nominal for the upper end of the cycle and the time  $T_s$  is +5 °C to -10 °C of  $T_{s(\text{min})}$  nominal for the lower end of the cycle.

**2.10** soak temperature: The temperature range that is -5 °C to +10/+15 °C (dependent on the Test Condition tolerance) of  $T_{s(max)}$  nominal and +5 °C to -10 °C of  $T_{s(min)}$  nominal.

**2.11** (temperature) cycle time: The time interval between one hi gh-temperature extreme to the next, or from one low-temperature extreme to the next, for a given sample; see Figure 1.

**2.12 ramp rate:** The rate of tem perature increase or decrease per unit of tim e for the sample(s).

NOTE 1 Ramp rate should be measured for the linear portion of the profile curve, which is generally the range between 10% and 90% of the test condition temperature range; see points **a** and **b** in Figure 1.

NOTE 2 Ramp rate can be load dependent and should be verified for the load being tested.

**2.13 test conditions:** The various temperature cycle range options listed in Table 1.

**2.14** soak mode: The categorization nomenclature that defines m inimum soak time at soak temperature(max) & soak temperature(min) in minutes.

NOTE 1 Each Test Condition will have four possible Soak Modes. These So ak Modes are listed in Table 2.

NOTE 2 The soak mode selected is dependent on the failure mechanism of interest.

**2.15** nominal  $T_{s(max)}$ : The temperature of the sample required to meet the maximum nominal temperature for a specific test condition; see Table 1.

**2.16** nominal  $T_{s(\min)}$ : The temperature of the sample required to meet the minimum nominal temperature for a specific test condition; see Table 1.

#### **3** Reference documents

JEP 140, Beaded Thermocouple Measurement of Semiconductor Packages.

JEP 153, Characterization and Monitoring of thermal Stress Test Oven Temperatures.

JESD94, Application Specific Qualification using Knowledge Based Test Methodology.

IPC-SM-785, Guidelines for Accelerated Reliability Testing of Surface Mount Solder Attachments.

#### 4 Apparatus

The chamber(s) used shall be capable of providing and controlling the specified temperatures and cycle timing in the working zone(s), when the chamber is loaded with a maximum load. Direct heat conduction to sam ple(s) shall be minimized. The capability of each cham ber achieving the sample temperature requirements shall be verified across each chamber by one or both of the following methods:

- a) Periodic calibration using instrumented parts and a maximum load, and continual monitoring during each test of such fixed tool therm ocouple temperature measurement(s) as adequate to ensure run-to-run repeatability.

- b) Continual monitoring during each test of an in strumented part or parts p laced at worst-case temperature locations (for example, this may be the corners and middle of the load).

#### 5 Procedure

Sample(s) shall be placed in such a position with respect to the air s tream such that there is substantially no obstruction to the flow of air across and aro und each sample(s). When special mounting is required, it shall be specified. The sample shall then be subjected to the specified temperature cycling test condition for the specified number of cycles (e.g., JE SD47 for qualification or as agreed to between the supplier and user). Completion of the total number of cycles specified for the test m ay be interrupt ed for interim end-point testing, test cham ber loading or unloading of device lots, electrical test of samples at specified intervals or as the result of power or equipment failure. However, if the aggregate number of times of all interrup tions exceeds 10% of the total number of cycles specified to the sample body, the am ount of glue or tape used shall be minimized to insure proper temperature measurements. The thermocouple, or equivalent temperature measurement apparatus, attachment method used should ensure that the entire m ass of the sample(s) is reaching the temperature extremes and the soak requirements.

# 5.1 Nominal cycle rates

Nominal cycle rates are dependent on the Soak Mode selected.

# 5.1.1 Component cycle rates

Typical component level temperature cycle rates are in the range of 1 to 3 cycles per hour (cph). Typical failure mechanisms include, but are not limited to, fatigue (such as metal circuit fatigue) and delamination. For certain failure m echanisms, such as ball bond integrity, faster rates, >3 cph can be used, if the tem perature cycling chambers are capable of meeting the  $T_s$  nominal and soak requirements for the given Test Condition.

# 5.1.2 Solder interconnect cycle rates

Typical solder interconnect cycle rates are slower, in the range of 1 to 2 cph, when solder joint fatigue evaluations are performed. These include flip chip, ball grid array and stack ed packages with solder interconnections. Cycle frequency and soak time is more significant for solder interconnections.

# 5.1.3 Tin whisker cycle rate

Tin whisker cycle rate shall be about 3 cycles per hour as stated in JESD22-A121.

Test Method A104E (Revision of Test Method A104D)

# 5.2 Maximum and minimum temperature

The maximum and minimum sample temperatures measured shall be within the range stated in Table 1 for the specific test condition being used. Typical boundary values of  $\pm 10^{\circ}$ C for  $T_{s(max)}$  and  $\pm 10^{\circ}$ C for  $T_{s(min)}$  are discretionary and depending on equipment capability and test objectives.

| Table 1 — Ten | perature cycling                | test conditions         |

|---------------|---------------------------------|-------------------------|

| Test          | Nominal                         | Nominal                 |

| Condition*    | $T_{\rm s(min)}(^{\circ}\rm C)$ | $T_{s(max)}(^{\circ}C)$ |

| A             | -55                             | +85                     |

| В             | -55                             | +125                    |

| С             | -65                             | +150                    |

| G             | -40                             | +125                    |

| H             | -55                             | +150                    |

| Ι             | -40                             | +115                    |

| J             | -0                              | +100                    |

| Κ             | -0                              | +125                    |

| L             | -55                             | +110                    |

| М             | -40                             | +150                    |

| Ν             | -40                             | +85                     |

| R             | -25                             | +125                    |

| Т             | -40                             | +100                    |

|               |                                 |                         |

**\*CAUTION**: Care should be taken when selecting Test Conditions, since: 1) the  $T_{s(max)}$  requirement for a specific Test Condition may exceed the glass tr ansition temperature of some package materials which may induce failure mechanisms not normally seen during design application conditions in the field, 2) large thermal gradients between and across the devices under test (DUT) need to be avoided in order to preserve the test data integrit y and 3) CTE differences over the test condition temperature range can produce premature failure of plated throug h holes in the test board, thus limiting electrical readout capability for the parts on test. Test Conditions that exceed 125 °C for  $T_{s(max)}$  are not recommended to Pb/Sn solder compositions due to potential dynamic recrystallization.

Selection of the therm al cycling test condition should correspond with its test objective, and application use condition. In som e cases, characterization of material responses to the extrem e temperatures for the chosen test selection may be critical to avoi d unintended outcom es as mentioned above.

Thermal cycling profiles commonly used for device qualification are referenced in JE SD47; yet, any other profile listed in this document (or custom profiles) may be utilized in accordance with JESD94 (knowledge based test methodology) or investigative purposes.

NOTE Temperature cycling test conditions differ ent from Table 1 can be used. Ho wever, test conditions should m eet the soak, c ycles per hour a nd ramp rate recommendations for the failure mechanism being tested. These conditions must be documented as indicated in 7(f).

|           | Table 2 — Soak mode conditions                    |

|-----------|---------------------------------------------------|

| Soak Mode | Minimum Soak Time at Soak Temperature(max) & Soak |

|           | Temperature(min) (minutes)                        |

| 1         |                                                   |

| 2         | 5                                                 |

| 3         | 10                                                |

| 4         | 15                                                |

# 5.2 Maximum and minimum temperature (cont'd)

NOTE Soak Modes different from Table 2 can be used, however, test conditions should be appropriate for the failure mechanism being tested. These conditions must be documented as indicated in 7(f).

# 5.3 Upper and lower soak times

Upper and Lower Soak Tim es vary by the Soak M ode selected; see Table 2. During this soak time the specimen shall reach the required nominal temperature, either  $T_{s(max)}$  or  $T_{s(min)}$ .

# 5.4 Upper and lower soak temperatures

Upper and Lower Soak Temperatures vary with the Test Condition selected; see Table 1.

# 5.5 Soak modes

Soak Modes are listed in Table 2. Soak Modes with longer soak times than those shown in Table 2 are not com patible with standard cycle rate s and should be selected only as required for a specific failure mechanism.

# 5.5.1 Component soak mode

In component temperature cycling, Soak Mode 1 is typically used.

# 5.5.2 Interconnect soak mode

Soak Modes 2, 3 and 4 are generally used for sold er fatigue and creep testing associated with interconnections such as flip chip or BGA solder joints.

# 5.5.3 Tin whisker soak mode

Tin whisker soak mode shall be 5 to 10 minutes as stated in JESD22-A121. This equates to soak mode 2, see Table 2.

#### 5.6 Nominal cycle time

Nominal cycle times vary with the Soak Mode selected. Table 3 lis ts typical cycle rates for components versus test condition and soak m ode. For solder interconnections, cycle tim es less than 30 minutes are not recommended.

| Table 5 — Typical frequency and soak mode for test conditions |                    |                   |  |

|---------------------------------------------------------------|--------------------|-------------------|--|

| Condition                                                     | Typical Cycles/Hr. | Typical Soak Mode |  |

| Α                                                             | 2-3                | 1, 2 & 3          |  |

| В                                                             | 2 - 3              | 1 & 2             |  |

| С                                                             | 2                  | 1 & 2             |  |

| G                                                             | < 1 - 2            | 1, 2, 3 & 4       |  |

| Н                                                             | 2                  | 1 & 2             |  |

| Ι                                                             | 1 - 2              | 1, 2, 3 & 4       |  |

| J                                                             | 1 - 3              | 1, 2, 3 & 4       |  |

| Κ                                                             | 1 - 3              | 1, 2, 3 & 4       |  |

| L                                                             | 1 - 3              | 1, 2, 3 & 4       |  |

| М                                                             | 1 - 3              | 1, 2, 3 & 4       |  |

| Ν                                                             | 1 - 3              | 1, 2 & 3          |  |

| R                                                             | 1 - 2              | 1 & 2             |  |

| Т                                                             | 1 - 2              | 3 & 4             |  |

| Table 5 — Typical frequency and soak mode for test conditions | Table 3 — | - Typical frequency | and soak mode for test conditions |

|---------------------------------------------------------------|-----------|---------------------|-----------------------------------|

|---------------------------------------------------------------|-----------|---------------------|-----------------------------------|

#### 5.7 Ramp rate

#### 5.7.1 Component ramp rate

Ramp rate is not critical for m ost component testing with the exception of interconnects, see 5.7.2.

#### 5.7.2 Interconnect ramp rate

When testing interconnections for solder joint fatigue, it is important to avoid transient therm al gradients in the sam ples on test. Sam ples with large thermal mass and low heat tr ansfer efficiency require ramp rates slow enough to compensate for the thermal mass. The temperature of the sample should be within a few degrees of the ambient temperature during the temperature ramps. Typical ramp rate for this situation is 15 °C/minute or less for any portion of the cycle, with a preferred rate of 10 °C to 14 °C/minute. For sam ples of large thermal mass, use of a single zone chamber may be required to achieve the best ramp rate.

NOTE 1 The preferred cycle rate is based on a balance between proper testing for solder joint fatigue and thermal cycling test efficiency.

NOTE 2 Air to air or li quid to liquid thermal shock chambers should not be substituted for therm al cycling chambers since the ramp rate of the DUT is important and too fast a rate can produce unrealistic damage during interconnect testing. Also large ther mal gradients on the DUT (s) can result in a varied acceleration factor across the chamber load.

NOTE 3 It is critical to control ramp rates as one may involuntarily generate a thermal shock test environment should the stated guidance be surpassed.

#### 5.7.2 Interconnect ramp rate (cont'd)

Typical test requirements for solder interconnection are listed in Table 4. The combination of ramp rate and soak time are important when testing solder interconnections.

| Table 4 — Recommended tes | t conditions for solde | r interconnection ter | nperature cycling  |

|---------------------------|------------------------|-----------------------|--------------------|

| Tuble 4 Recommended tes   | conditions for soluc.  | i mici comiccuon tei  | nper atur e cyenng |

|   |                  |           |                        | 1 0              |

|---|------------------|-----------|------------------------|------------------|

| Т | 'est Condition*  | Soak Mode | Ramp Rate (°C/minute)  | Cycle Rate (cph) |

| ( | G, I, J, K, L, T | 2         | Thermal Mass Dependent | 2                |

| ( | G, I, J, K, L, T | 3         | Thermal Mass Dependent | ≤2               |

| ( | G, I, J, K, L, T | 4         | Thermal Mass Dependent | <1               |

|   | R                | 1         | Thermal Mass Dependent | 2                |

\* **CAUTION**: Care should be taken in selection of Test Conditions s ince the  $T_{s(min)}$  may cause cracking of the Printed W iring Board plated through holes and/ or wiring, thus inhibiting electrical readouts associated with the solder interconnections being tested.

#### **5.8** Load transfer time (Dual chamber only)

Load transfer time shall be less than 1 minute, in order to maintain a uniform temperature profile across the load.

#### 5.9 Measurements

Visual examination and electrical m easurements, which consists of param etric and functional test, shall be performed as specified in the ap plicable procurement document or data sheet. Electrical test may be performed either in-situ or at an ambient or extreme temperature. Failure resistance criteria must be adjusted based on the temperature of the sample at time of test. In addition, hermeticity test(s) per JESD22-A109 shall also be performed for hermetic devices.

#### 6 Failure criteria

Failure criteria shall include, but not be lim ited to, hermeticity for hermetic devices, parametric limits, functional limits, mechanical damage and warpage. Parametric and functional limits shall be defined by the applicable procurem ent document. M echanical damage shall not include damage induced by fixturing or handling or the damage is not critical to the package performance in the specific application.

Test Method A104E (Revision of Test Method A104D)

#### 7 Summary

The following details shall be specified in the applicable procurement documents:

- a) Special mounting, if applicable; see section 4.

- b) Temperature extremes; see Table 1, soak time; see Table 2, sample cooling and heating ramp rate and number of cycles, or specific component requirements.

- c) Interim measurement intervals, when required.

- d) Special acceptance criteria for examinations, seal tests (for hermetic packages), internal bond integrity tests and electrical tests if other than those specified in the device specification.

- e) For qualification testing, sample size and quality level.

- f) Temperature extremes other than in Table 1. Specify the num ber of cycles, temperature extremes, soak time, cycles per hour, tolerance on temperature extremes (if different from Table 1), ramp rate and interim measurements, if required.

Time (minutes)

Figure 1 — Representative temperature profile for thermal cycle test conditions

NOTE Ramp rate should be measured for the linear portion of the profile curve, which is generally the range between 10% and 90% of the Test Condition temperature range; see points a and b in Figure 1.

#### Annex B (informative) Differences between JESD22-A104E and JESD22-A104D

This table briefly describes most of the changes made to entries that appear in this standard, JESD22A104E, compared to its predecessor, JESD22-A104D (March 2009). If the change to a concept involves any words added or deleted (excluding deletion of accidentally repeated words), it is included. Some punctuation changes are not included.

| Clause | Description of change                                                                                                                                                                                                                                                        |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3      | <ul> <li>Terms and Definition</li> <li>Added JESD94 reference</li> <li>Added IPC-SM-785 reference</li> </ul>                                                                                                                                                                 |

| 5.2    | <ul> <li>Revise Table 1</li> <li>added (2) new T/C profile – TCR, TCT</li> <li>Revise column (Upper and Lower tolerances)</li> <li>Test condition selection considerations</li> <li>Ref. to JESD47 and other considerations for thermal cycling profile selection</li> </ul> |

| 5.6    | Revise table 3<br>- Soak recommendations for (2) new T/C profile – TCR, TCT                                                                                                                                                                                                  |

| 5.7.2  | Revise table 4<br>– Solder interconnect recommendations for (2) new T/C profile – TCR, TCT                                                                                                                                                                                   |

JEDEC Standard No. 22-A104E Page 12

# **Standard Improvement Form**

JEDEC

The purpose of this form is to provide the Technical Committees of JEDEC with input from the industry regarding usage of the subject standard. Individuals or companies are invited to submit comments to JEDEC. All comments will be collected and dispersed to the appropriate committee(s).

If you can provide input, please complete this form and return to:

| JEDEC<br>Attn: Publications Department<br>2500 Wilson Blvd. Suite 220<br>Arlington, VA 22201-3834<br>Fax: 703.907.7583       |  |  |

|------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1. I recommend changes to the following:         Requirement, clause number         Test method number         Clause number |  |  |

| The referenced clause number has proven to be: Unclear Too Rigid In Error Other                                              |  |  |

| 2. Recommendations for correction:                                                                                           |  |  |

|                                                                                                                              |  |  |

| 3. Other suggestions for document improvement:                                                                               |  |  |

| Submitted by Name: Phone:                                                                                                    |  |  |

| Company: E-mail:                                                                                                             |  |  |

| Address:                                                                                                                     |  |  |

| City/State/Zip: Date:                                                                                                        |  |  |