# JEDEC STANDARD

## IC Latch-Up Test

JESD78E (Revision of JESD78D, November 2011)

APRIL 2016

JEDEC SOLID STATE TECHNOLOGY ASSOCIATION

Downloaded by xu vajun (xuyi@beice-sh.com) on Jan 19, 2020, 5:09 am PST 联系方式:xuyi@beice-sh.com 1391716567

#### NOTICE

JEDEC standards and publications contain material that has been prepared, reviewed, and approved through the JEDEC Board of Directors level and subsequently reviewed and approved by the JEDEC legal counsel.

JEDEC standards and publications are designed to serve the public interest through eliminating misunderstandings between manufacturers and purchasers, facilitating interchangeability and improvement of products, and assisting the purchaser in selecting and obtaining with minimum delay the proper product for use by those other than JEDEC members, whether the standard is to be used either domestically or internationally.

JEDEC standards and publications are adopted without regard to whether or not their adoption may involve patents or articles, materials, or processes. By such action JEDEC does not assume any liability to any patent owner, nor does it assume any obligation whatever to parties adopting the JEDEC standards or publications.

The information included in JEDEC standards and publications represents a sound approach to product specification and application, principally from the solid state device manufacturer viewpoint. Within the JEDEC organization there are procedures whereby a JEDEC standard or publication may be further processed and ultimately become an ANSI standard.

No claims to be in conformance with this standard may be made unless all requirements stated in the standard are met.

Inquiries, comments, and suggestions relative to the content of this JEDEC standard or publication should be addressed to JEDEC at the address below, or refer to <u>www.jedec.org</u> under Standards and Documents for alternative contact information.

Published by ©JEDEC Solid State Technology Association 2016 3103 North 10th Street Suite 240 South Arlington, VA 22201-2107

This document may be downloaded free of charge; however JEDEC retains the copyright on this material. By downloading this file the individual agrees not to charge for or resell the resulting material.

#### **PRICE: Contact JEDEC**

Printed in the U.S.A. All rights reserved

Bernsonnor

Downloaded by xu vajun (xuyi@beice-sh.com) on Jan 19, 2020, 5:09 am PST 联系方式:xuyi@beice-sh.com 1391716567

## IC LATCH-UP TEST

#### Contents

| 1                                                                                                                                                                                            | Scope                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| 1.1                                                                                                                                                                                          | Classification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                               |

| 1.2                                                                                                                                                                                          | Latch-up immunity characterization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 2                                                                           |

| •                                                                                                                                                                                            | Terms and definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | •                                                                             |

| 2                                                                                                                                                                                            | Terms and definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | .2                                                                            |

| 3                                                                                                                                                                                            | Apparatus and material                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5                                                                             |

| 3<br>3.1                                                                                                                                                                                     | Latch-up tester.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | • 5<br>5                                                                      |

| 3.2                                                                                                                                                                                          | Automated test equipment (ATE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                               |

| 3.3                                                                                                                                                                                          | Heat source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                               |

| 5.5                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                               |

| 4                                                                                                                                                                                            | Procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 6                                                                           |

| 4.1                                                                                                                                                                                          | General latch-up test procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                               |

| 4.2                                                                                                                                                                                          | Detailed latch-up test procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                               |

| 4.2.1                                                                                                                                                                                        | I-test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                               |

| 4.2.1.1                                                                                                                                                                                      | Supply current limits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                               |

| 4.2.2                                                                                                                                                                                        | V <sub>supply</sub> overvoltage test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 13                                                                            |

| 4.2.3                                                                                                                                                                                        | Testing dynamic devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                               |

| 4.2.4                                                                                                                                                                                        | DUT disposition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                               |

| 4.2.5                                                                                                                                                                                        | Record keeping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 16                                                                            |

|                                                                                                                                                                                              | Latch-up detection criteria                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                               |

| 5                                                                                                                                                                                            | Latch-up detection criteria                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 16                                                                            |

|                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                               |

| 1                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1 7                                                                           |

| 6                                                                                                                                                                                            | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 17                                                                            |

|                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                               |

| Tables                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                               |

| <b>Tables</b>                                                                                                                                                                                | Latch-up Immunity Levels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 2                                                                           |

| Tables<br>1<br>2                                                                                                                                                                             | Latch-up Immunity Levels<br>Test Matrix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 2<br>. 7                                                                    |

| <b>Tables</b>                                                                                                                                                                                | Latch-up Immunity Levels<br>Test Matrix<br>Timing specifications for I-test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 2<br>. 7<br>10                                                              |

| Tables<br>1<br>2<br>3                                                                                                                                                                        | Latch-up Immunity Levels<br>Test Matrix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 2<br>. 7<br>10                                                              |

| <b>Tables</b> 1 2 3 4                                                                                                                                                                        | Latch-up Immunity Levels<br>Test Matrix<br>Timing specifications for I-test<br>Timing specifications for V <sub>supply</sub> overvoltage test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 2<br>. 7<br>10<br>14                                                        |

| Tables<br>1<br>2<br>3                                                                                                                                                                        | Latch-up Immunity Levels<br>Test Matrix<br>Timing specifications for I-test<br>Timing specifications for V <sub>supply</sub> overvoltage test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 2<br>. 7<br>10<br>14                                                        |

| Tables<br>1<br>2<br>3<br>4<br>Figures                                                                                                                                                        | Latch-up Immunity Levels<br>Test Matrix<br>Timing specifications for I-test<br>Timing specifications for V <sub>supply</sub> overvoltage test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 2<br>. 7<br>10<br>14                                                        |

| Tables         1           2         3           4         Figures           1         1                                                                                                     | Latch-up Immunity Levels<br>Test Matrix<br>Timing specifications for I-test<br>Timing specifications for V <sub>supply</sub> overvoltage test<br>s<br>Typical Latch-up test flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 2<br>. 7<br>10<br>14<br>. 6                                                 |

| Tables           1           2           3           4           Figures           1           2                                                                                             | Latch-up Immunity Levels<br>Test Matrix<br>Timing specifications for I-test<br>Timing specifications for V <sub>supply</sub> overvoltage test<br>s<br>Typical Latch-up test flow<br>Test waveform for positive I-test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 2<br>. 7<br>10<br>14<br>. 6<br>. 9                                          |

| Tables           1           2           3           4           Figures           1           2           3           4                                                                     | Latch-up Immunity Levels<br>Test Matrix<br>Timing specifications for I-test<br>Timing specifications for V <sub>supply</sub> overvoltage test<br><b>s</b><br>Typical Latch-up test flow<br>Test waveform for positive I-test<br>Test waveform for negative I-test<br>The equivalent circuit for positive input/output I-test latch-up testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 2<br>. 7<br>10<br>14<br>. 6<br>. 9<br>. 9                                   |

| Tables         1           2         3           4         Figures           1         2           3         4           4         4                                                         | Latch-up Immunity Levels<br>Test Matrix<br>Timing specifications for I-test<br>Timing specifications for V <sub>supply</sub> overvoltage test<br><b>s</b><br>Typical Latch-up test flow<br>Test waveform for positive I-test<br>Test waveform for negative I-test<br>The equivalent circuit for positive input/output I-test latch-up testing<br>The equivalent circuit for negative input/output I-test latch-up testing                                                                                                                                                                                                                                                                                                                                                                                    | . 2<br>. 7<br>10<br>14<br>. 6<br>. 9<br>. 9<br>10<br>11                       |

| Tables           1           2           3           4           Figures           1           2           3           4           5                                                         | Latch-up Immunity Levels<br>Test Matrix<br>Timing specifications for I-test<br>Timing specifications for V <sub>supply</sub> overvoltage test<br>s<br>Typical Latch-up test flow<br>Test waveform for positive I-test<br>Test waveform for negative I-test<br>The equivalent circuit for positive input/output I-test latch-up testing<br>The equivalent circuit for negative input/output I-test latch-up testing<br>Test waveform for V <sub>supply</sub> overvoltage test                                                                                                                                                                                                                                                                                                                                 | . 2<br>. 7<br>10<br>14<br>. 6<br>. 9<br>. 9<br>10<br>11                       |

| Tables           1           2           3           4           Figures           1           2           3           4           5           6                                             | Latch-up Immunity Levels<br>Test Matrix<br>Timing specifications for I-test<br>Timing specifications for V <sub>supply</sub> overvoltage test<br><b>s</b><br>Typical Latch-up test flow<br>Test waveform for positive I-test<br>Test waveform for negative I-test<br>The equivalent circuit for positive input/output I-test latch-up testing<br>The equivalent circuit for negative input/output I-test latch-up testing                                                                                                                                                                                                                                                                                                                                                                                    | . 2<br>. 7<br>10<br>14<br>. 6<br>. 9<br>. 9<br>10<br>11                       |

| Tables           1           2           3           4           Figures           1           2           3           4           5           6           7                                 | Latch-up Immunity Levels<br>Test Matrix<br>Timing specifications for I-test<br>Timing specifications for V <sub>supply</sub> overvoltage test<br><b>s</b><br>Typical Latch-up test flow<br>Test waveform for positive I-test<br>Test waveform for negative I-test<br>The equivalent circuit for positive input/output I-test latch-up testing<br>The equivalent circuit for negative input/output I-test latch-up testing<br>Test waveform for V <sub>supply</sub> overvoltage test<br>The equivalent circuit for N <sub>supply</sub> overvoltage test                                                                                                                                                                                                                                                       | . 2<br>. 7<br>10<br>14<br>. 9<br>. 9<br>10<br>11<br>14<br>15                  |

| Tables           1           2           3           4           Figures           1           2           3           4           5           6           7           Annex                 | Latch-up Immunity Levels<br>Test Matrix<br>Timing specifications for I-test<br>Timing specifications for V <sub>supply</sub> overvoltage test<br>s<br>Typical Latch-up test flow<br>Test waveform for positive I-test<br>Test waveform for negative I-test<br>The equivalent circuit for positive input/output I-test latch-up testing<br>The equivalent circuit for negative input/output I-test latch-up testing<br>Test waveform for V <sub>supply</sub> overvoltage test<br>The equivalent circuit for N <sub>supply</sub> overvoltage test<br>The equivalent circuit for V <sub>supply</sub> overvoltage test latch-up testing<br>The equivalent circuit for V <sub>supply</sub> overvoltage test latch-up testing<br>A (informative) Examples of special pins that are connected to passive components | . 2<br>. 7<br>10<br>14<br>. 9<br>. 9<br>10<br>11<br>14<br>15                  |

| Tables           1           2           3           4           Figures           1           2           3           4           5           6           7           Annex           Annex | Latch-up Immunity Levels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 2<br>. 7<br>10<br>14<br>. 9<br>. 9<br>10<br>11<br>14<br>15<br><b>18</b>     |

| Tables           1           2           3           4           Figures           1           2           3           4           5           6           7           Annex           Given | Latch-up Immunity Levels<br>Test Matrix<br>Timing specifications for I-test<br>Timing specifications for V <sub>supply</sub> overvoltage test<br>s<br>Typical Latch-up test flow<br>Test waveform for positive I-test<br>Test waveform for negative I-test<br>The equivalent circuit for positive input/output I-test latch-up testing<br>The equivalent circuit for negative input/output I-test latch-up testing<br>Test waveform for V <sub>supply</sub> overvoltage test<br>The equivalent circuit for N <sub>supply</sub> overvoltage test<br>The equivalent circuit for V <sub>supply</sub> overvoltage test latch-up testing<br>The equivalent circuit for V <sub>supply</sub> overvoltage test latch-up testing<br>A (informative) Examples of special pins that are connected to passive components | . 2<br>.7<br>10<br>14<br>. 6<br>.9<br>10<br>11<br>14<br>15<br><b>18</b><br>20 |

## IC LATCH-UP TEST

(From JEDEC Board Ballots JCB-16-08, formulated under the cognizance of JC-14.1 Subcommittee on Reliability Test Methods for Packaged Devices.)

| 1 Scope |

|---------|

|---------|

This standard covers the I-test and V<sub>supply</sub> overvoltage latch-up testing of integrated circuits.

The purpose of this standard is to establish a method for determining IC latch-up characteristics and to define latch-up detection criteria. Latch-up characteristics are extremely important in determining product reliability and minimizing No Trouble Found (NTF) and Electrical Overstress (EOS) failures due to latch-up. This test method is applicable to NMOS, CMOS, bipolar, and all variations and combinations of these technologies.

NOTE As these technologies have evolved, it has been necessary to adjust this document to the realities of characterization with limits not imagined when the first latch-up document was generated some 25 years ago. Though it would be simpler to make the original limits of 1.5 times the maximum pin operating voltage an absolute level of goodness, the possibilities of success at this level are limited by the very low voltage technologies, and the medium and high voltage CMOS, BiCMOS and Bipolar technologies (>12 V). The concept of maximum stress voltage (MSV) allows the supplier to characterize latch-up in a way that differentiates between latch-up and EOS. This revision will make it more transparent to the end user that given the limits of certain technologies the subsequent latch-up characterizations are valid.

#### 1.1 Classification

There are two classes for latch-up testing.

- Class I is for testing at room temperature ambient.

- Class II is for testing at the maximum operating ambient temperature  $(T_a)$  or maximum operating case temperature  $(T_c)$  or maximum operating junction temperature  $(T_j)$  in the data sheet.

For Class II testing at the maximum operating  $T_a$  or  $T_c$ , the ambient temperature or case temperature ( $T_c$ ) shall be established at the required test value. For Class II testing at the maximum operating  $T_j$ , the ambient temperature  $T_a$  or the case temperature  $T_c$  should be selected to achieve a temperature characteristic of the junction temperature for a given device operating mode(s) during latch-up testing. The maximum operating ambient or case temperature during stress may be calculated based on the methods detailed in Annex B. The values used in Class II testing shall be recorded in the final report.

NOTE Elevated temperature will reduce latch-up resistance, and class II testing is recommended for devices that are required to operate at elevated temperature.

#### 1.2 Latch-up immunity characterization

Product latch-up immunity is characterized by an I/O current injection value and  $V_{supply}$  overvoltage value that does not result in a latch-up as defined in this test method. Refer to Table 1 for the recommended range of current and voltage stress, and Table 2 footnotes b, c, and d for the clamping conditions. The actual achieved force current or voltage levels may be reported as mentioned in Annex C.

| Table 1 — Latch-up immunity levels                                                                                                                                                                                                                                                                          |                                          |                                                  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--------------------------------------------------|--|--|--|--|

| Immunity Level                                                                                                                                                                                                                                                                                              | Test                                     | Magnitude of Trigger Force Current<br>or Voltage |  |  |  |  |

|                                                                                                                                                                                                                                                                                                             | Positive I-Test                          | $\geq 100 \text{ mA}^{a}$                        |  |  |  |  |

| Α                                                                                                                                                                                                                                                                                                           | Negative I-Test                          | $\geq 100 \text{ mA}^{a}$                        |  |  |  |  |

|                                                                                                                                                                                                                                                                                                             | Overvoltage Test                         | 1.5 x VDD or MSV, whichever is less <sup>b</sup> |  |  |  |  |

| в                                                                                                                                                                                                                                                                                                           | B If immunity level A cannot be achieved |                                                  |  |  |  |  |

| <sup>a</sup> The actual injected current may be less than 100mA if pin voltage clamping limits are<br>reached (See Table 2). If Latch-up does not occur in such a condition, then this constitutes a<br>passing test with Immunity Level A. Otherwise, it is classified with Immunity Level B.              |                                          |                                                  |  |  |  |  |

| <sup>b</sup> The actual applied voltage may be less than 1.5 x VDD or MSV if $V_{supply}$ current clamping limits are reached (See Table 2). If Latch-up does not occur in such a condition, then this constitutes a passing test with Immunity Level A. Otherwise, it is classified with Immunity Level B. |                                          |                                                  |  |  |  |  |

| Table 1 — Latch-up | immunity levels |

|--------------------|-----------------|

|--------------------|-----------------|

#### 2 Terms and definitions

The following terms and definitions apply to this test method.

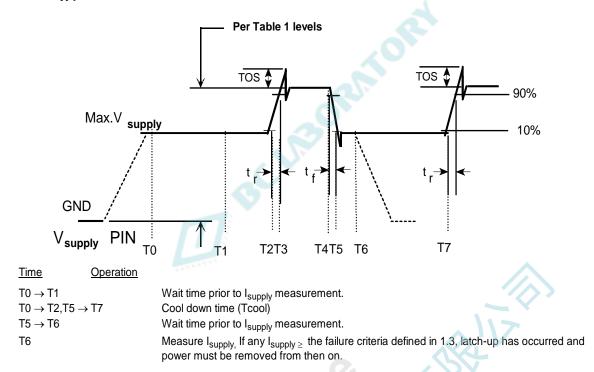

**cool-down time:** The period of time between successive applications of trigger pulses, or the period of time between the removal of the  $V_{supply}$  voltage and the application of the next trigger pulse. (See Figure 2, Figure 3, Figure 6, and Table 3.)

**DUT:** The device under test.

dynamic devices: Devices requiring clocking in order to guarantee a stable state while being tested.

**GND** (Ground): The common or zero-potential pin(s) of the DUT.

NOTE 1 Ground pins are not latch-up tested. NOTE 2 A ground pin is sometimes called V<sub>ss</sub>.

**input pins:** All address, data-in control, V<sub>ref</sub>, and similar pins.

**I/O** (**bidirectional**) **pins:** Device pins that can be made to operate as an input or an output or in a high-impedance state.

#### 2 Terms and definitions (cont'd)

**Isupply:** The total supply current in each  $V_{supply}$  pin (or pin group) with the DUT biased as indicated in Table 2.

I-test: A latch-up test that supplies positive and negative current pulses to the pin under test.

**latch-up:** A state in which a low-impedance path, resulting from an overstress that triggers a parasitic thyristor structure, persists after removal or cessation of the triggering condition.

NOTE 1 The overstress can be a voltage or current surge, an excessive rate of change of current or voltage, or any other abnormal condition that causes the parasitic thyristor structure to become regenerative.

NOTE 2 Latch-up will not damage the device provided that the current through the low-impedance path is sufficiently limited in magnitude or duration.

**logic-high:** A level within the more positive (less negative) of the two ranges of logic levels chosen to represent the logic states.

NOTE 1 For digital devices, the maximum value of the high logic level voltage is used for latch-up testing. The maximum logic high level is designated as  $V_{max}$ .

NOTE 2 For non-digital devices, the maximum operating voltage that can be applied to that pin as defined in the device specification is used for latch-up testing.

**logic-low:** A level within the more negative (less positive) of the two ranges of logic levels chosen to represent the logic states.

NOTE 1 For digital devices, the minimum value of the low logic level voltage is used for latch-up testing. The minimum logic low level is designated as  $V_{min}$ .

NOTE 2 For non-digital devices, the minimum operating voltage that can be applied to that pin as defined in the device specification is used for latch-up testing.

**maximum**  $V_{supply}$ ; **maximum operating voltage:** The maximum supply voltage at which a device is specified to operate in compliance with the applicable device specification.

NOTE 1 "Maximum" refers to the magnitude of supply voltage and can be either positive or negative.

NOTE 2 The maximum voltage is not the absolute maximum rated voltage, i.e., the voltage beyond which permanent damage is likely.

#### 2 Terms and definitions (cont'd)

**maximum stress voltage (MSV)**: The maximum voltage allowed to be placed on any given pin during latch-up immunity testing without causing irreversible damage to the device from a catastrophic breakdown of the silicon device or circuit not related to latch-up.

NOTE 1 A positive MSV is higher than the maximum operating voltage and a negative MSV is lower than the minimum operating voltage.

NOTE 2 MSV is NOT the same as the absolute maximum voltage rating (AMR) from the device data sheet. MSV applies to latch-up testing only, protecting the DUT from physical damage from stress mechanisms not directly related to latch-up. An example of an unrelated stress is one exceeding the destructive breakdown voltage of a pin resulting in non-latch-up induced catastrophic breakdown of the silicon device / circuit. MSV may be different for each pin and each polarity during testing, depending on process technology and circuit topology. In many medium and high voltage designs (>12 V), MSV may be nearly the same value as AMR. Further, the MSV value depends on the pulse width used during latch-up testing. Shorter pulse widths may allow a higher value for MSV. Therefore, the MSV value chosen should take into account the pulse width as well as process technology and circuit topology.

**"no connect" pin:** A pin that has no internal connection and that can be used as a support for external wiring without disturbing the function of the device.

NOTE All "no connect" pins shall be left in an open (floating) state during latch-up testing.

**nominal**  $I_{supply}$  ( $I_{nom}$ ): The measured dc supply current for each  $V_{supply}$  pin (or pin group) with the DUT biased at the test temperature as defined in clause 4 and Table 2.

**output pin:** A device pin that generates a signal or voltage level as a normal function during the normal operation of the device.

NOTE Output pins, though left in an open (floating) state during testing of other pin types, are latch-up tested.

power supply: A component in the test system that supplies voltage and current to the DUT.

**preconditioned pin:** A device pin that has been placed in a defined state or condition (input, output, high impedance, etc.) by applying control vectors to the DUT.

**test condition:** The test temperature, supply voltage, current limits, voltage limits, clock frequency, input bias voltages, and preconditioning vectors applied to the DUT during the latch-up test.

**timing-related input pin:** A pin such as clock crystal oscillator, charge pump circuit, etc., required to place the DUT in a normal operating mode.

NOTE Required timing signals may be applied by the latch-up tester, external equipment, and/or external components as appropriate.

**trigger pulse:** The positive or negative current pulse (I-Test) or voltage pulse ( $V_{supply}$  overvoltage test) applied to any pin under test in an attempt to induce latch-up (see Figure 2, Figure 3 and Figure 6).

#### 2 Terms and definitions (cont'd)

**trigger duration:** The duration of an applied pulse from the trigger source. (See Figure 2, Figure 3, Figure 6 and Table 3.)

**Vsupply pin (or pin group):** A supply pin is any pin that provides current to a circuit. Supply pins typically transmit no information (such as digital or analog signals, timing, clock signals, voltage or current reference levels). For the purpose of latch-up testing, power pins are treated as supply pins.

NOTE 1 Generally, it is permissible to treat equal-potential voltage source pins as one  $V_{supply}$  pin (or pin group) and connect them to one power supply.

NOTE 2 When forming  $V_{supply}$  pins (or pin groups), the combination of  $V_{supply}$  pins with significantly different supply current levels is not recommended as this would make it difficult to detect significant current changes on low supply current pins.

$V_{supply}$  overvoltage test: A latch-up test that supplies overvoltage pulses to the  $V_{supply}$  pin (or pin group) under test.

#### 3 Apparatus and material

The apparatus required for this test method includes the following:

#### 3.1 Latch-up tester

Test equipment capable of performing the tests as specified in this document. For devices requiring dynamic testing, the test equipment shall be capable of supplying timing signals and logic setup vectors required to control the I/O pin output states as specified in 4.2.3. The required timing signals and logic vectors may be applied by the latch-up tester itself, external equipment, and/or external components as appropriate.

#### **3.2** Automated test equipment (ATE)

A device tester capable of performing full functional and parametric testing of the device to the device specification requirements.

#### 3.3 Heat source

Equipment capable of heating and maintaining the DUT at the maximum operating temperature specified in the device specification during the latch-up test.

#### 4 Procedure

#### 4.1 General latch-up test procedure

Prior to the latch-up test, the device needs to be in a stable state with reproducible  $I_{nom}$ . Engineering judgment may be needed to achieve sufficient stability. The supply current should be made as low as practicable. The supply current must be stable enough and low enough to reliably detect the supply current increase if latch-up occurs.

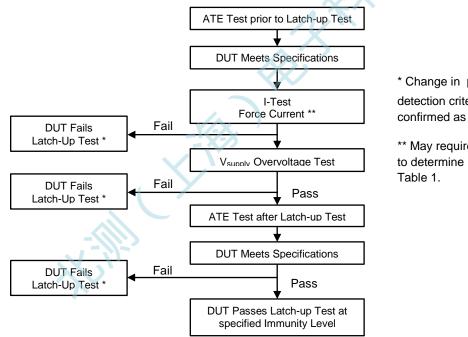

A minimum of three (3) devices shall be subjected to latch-up testing using the I-test and supply overvoltage test. It is allowed to partition I-test, supply overvoltage test, or test combinations by using at least 3 fresh devices for each partition. All devices to be latch-up tested must have passed ATE testing to the device specification requirements. Before latch-up testing, the device continuity in the socket should be checked to avoid false latch-up failures. The latch-up test flow shall be as shown in Figure 1. The devices to be tested shall be subjected to the test conditions specified in Table 2 and Table 3. All "no connect" pins on the DUT shall be left open (floating) at all times.

All pins on the DUT, with the exception of "no connect" pins and timing related pins, shall be latch-up tested. The Input, output, and configurable I/O pins are to be tested with the I-test and the  $V_{supply}$  pins tested with the Overvoltage test. This includes special pins defined in Annex A. The passing current or voltage values for the special pins can be used for determining the values of the passive-components connected to the pins. I/O pins shall be tested in all possible operating states or the worst case operating state (typically high impedance for configurable I/O pins). Dynamic devices shall be tested per 4.2.3. When a device is sufficiently complex that testing of all configurable I/O pins in the worst case condition is not practicable, the device should be conditioned with a set of vectors representative of the typical operation of the device as determined by engineering judgment. When an I/O pin cannot be tested in the high impedance state, the I/O shall be tested in a valid logic state. Untested pins and pins that could not be completely tested shall be recorded as specified in 4.2.5 and the user shall be informed of all I/O pins that were not tested or tested in all states. After latch-up testing, all devices must pass the criteria specified in Section 5.

\* Change in I<sub>Supply</sub> exceeds detection criteria in Table 2 and confirmed as a valid latch-up failure.

\*\* May require iterative current stress to determine Immunity Level from Table 1.

Figure 1 — Typical latch-up test flow

| 4.1 General latch-up test procedure (cont'd) | 4.1 | General latch-up test procedure ( | cont'd) |

|----------------------------------------------|-----|-----------------------------------|---------|

|----------------------------------------------|-----|-----------------------------------|---------|

|                                    | Table 2 — Test matrix'   |                                        |                                                                                                                   |                                                                                               |                                                                            |                                                         |  |  |

|------------------------------------|--------------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------|--|--|

| Test type                          | Trigger<br>polarity      | Condition of<br>untested input<br>pins | Test temperature classification                                                                                   | V <sub>supply</sub><br>conditions                                                             | Trigger test<br>conditions for<br>pin or supply<br>group under test        | Latch-up<br>detection<br>criteria <sup>5, 6</sup>       |  |  |

|                                    | POSITIVE                 | Max Logic<br>High <sup>1</sup>         | 3                                                                                                                 |                                                                                               | See Table 1 for<br>stress current range                                    | If absolute<br>I <sub>nom</sub> is                      |  |  |

| I-Test                             | see Figure 4             | Min Logic<br>Low <sup>1</sup>          | Temperature Class<br>I Room<br>Temperature<br>Temperature Class<br>II Maximum<br>ambient operating<br>temperature | Maximum<br>operating<br>voltage for<br>each<br>V <sub>supply</sub> pin<br>group per<br>device | and Note 3 for clamp voltage                                               | $\leq$ 25 mA,<br>then absolute<br>$I_{nom}$ + 10 mA is  |  |  |

|                                    | NEGATIVE<br>see Figure 5 | Max Logic<br>High <sup>1</sup>         |                                                                                                                   |                                                                                               | See Table 1 for<br>stress current range<br>and Note 4 for<br>clamp voltage | used                                                    |  |  |

|                                    |                          | Min Logic<br>Low <sup>1</sup>          |                                                                                                                   |                                                                                               |                                                                            | Or<br>If absolute                                       |  |  |

| V <sub>supply</sub><br>Overvoltage | See Figure 7             | Max Logic<br>High <sup>1</sup>         |                                                                                                                   |                                                                                               | See Table 1 for<br>stress voltage and                                      | I absolute<br>$I_{nom}$ is<br>> 25  mA,<br>then $> 1.4$ |  |  |

| test                               | Barris Barris            | Min Logic<br>Low <sup>1</sup>          |                                                                                                                   |                                                                                               | Note 2 for clamp<br>current                                                | X absolute I <sub>nom</sub><br>is used                  |  |  |

## **Table 2** — **Test matrix**<sup>7</sup>

NOTE 1 Max. logic high and min. logic low shall be per the device specification. When logic levels are used with respect to non-digital device it means the maximum high or minimum low voltage the can be supplied to the pin per the device specification.

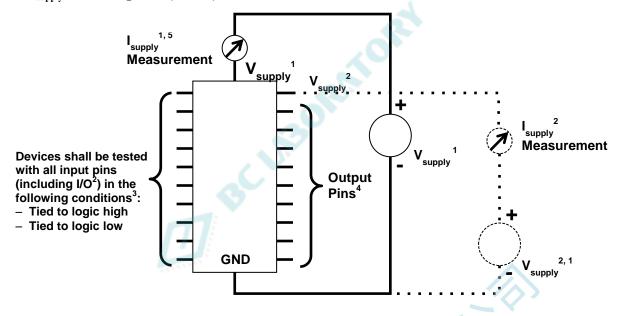

NOTE 2 During supply overvoltage latch-up tests, it is common to combine several IC supply pins of the same voltage into one supply group. It is necessary to combine supply pins into one group if they are connected internally. The current clamp for the supply group is set according to the total nominal supply current of the group. The clamp current for the j<sup>th</sup> supply group is the greater of: a. or b.

$\sum I_{nomi}$

a.

$$I_{clamp j} = 100 \ mA + I_{nom j} = 100 \ mA + \sum I_{nom i}$$

All supplies in supply group

$I_{clamp j} = 1.5 \times I_{nom j} = 1.5 \times$

NOTE 3 The pin clamping voltage for positive I-test is giving by  $V_{clamp} = V_{max} + 0.5x(V_{max} - V_{min})$  with an upper limit of  $1.5xV_{max}$ , where  $V_{max}$  (logic high) and  $V_{min}$  (logic low) are defined in Section 2. If the Maximum Stress Voltage (MSV) for the pin (See Section 2) is less than  $V_{max} + 0.5x(V_{max} - V_{min})$  or  $1.5xV_{max}$ , then the pin clamping voltage is given by  $V_{clamp} = MSV$ . In some instances the forcing current required and the voltage limit may have opposite polarities. Two- quadrant power supplies are not capable of providing positive injection current with negative clamping voltage. Four-quadrant power supplies do not share this limitation.

all supplies in supply group j

NOTE 4 The pin clamping voltage for negative I-test is given by  $V_{clamp} = V_{min} - 0.5x(V_{max} - V_{min})$  with a lower limit of  $-0.5xV_{max}$ , where  $V_{max}$  (logic high) and  $V_{min}$  (logic low) are defined in Section 2. If the Maximum Stress Voltage (MSV) for the pin is greater than  $V_{min} - 0.5x(V_{max} - V_{min})$  or  $-0.5xV_{max}$ , then the pin clamping voltage is given by  $V_{clamp} = MSV$ . In some instances the forcing current required and the voltage limit may have opposite polarities. Two- quadrant power supplies are not capable of providing negative injection current with positive clamping voltage. Four-quadrant power supplies do not share this limitation.

NOTE 5 If the trigger test condition reaches the voltage of current clamp limit and latch-up has not occurred, the pin passes the latchup test. See clause 5 for the complete failure definition.

NOTE 6 During I-test or supply overvoltage test, the supply currents for all supply groups are monitored for latch-up occurrence. Failure occurs if any supply current exceeds the limit in Table 2.

NOTE 7 The trigger conditions herein are not indicative of appropriate trigger conditions for all devices. Appropriate trigger conditions may be more or less stringent. When trigger conditions used in testing differ from this table, the trigger conditions used must be defined in the test results.

#### 4.2 Detailed latch-up test procedure

#### 4.2.1 I-test

The I-test shall be performed as follows:

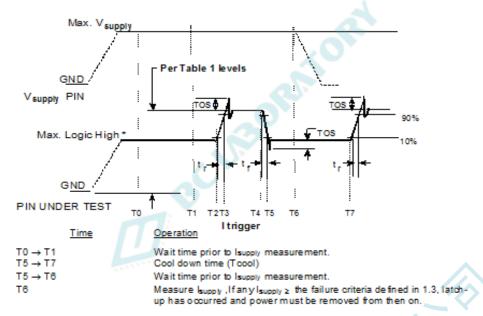

- 1) The devices shall be subjected to the I-test as indicated in Figure 1/Table 2 and Figure 2 and Figure 3/Table 3.

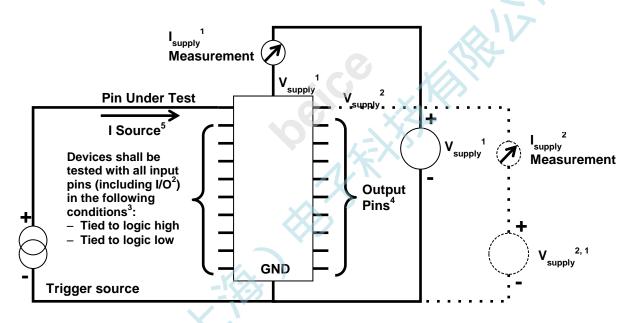

- 2) Bias the DUT as indicated in Figure 4. All input pins, including bi-directional I/O pins in an input state or high impedance state, not used for preconditioning the I/O pins, shall be tied to the maximum logichigh level specified in the device specification. Input pins used for preconditioning must be tested in their defined state (pins that are tied to a logic-high level to precondition the DUT can only be tested in the logic-high state; pins that are tied to a logic-low level to precondition the DUT can only be tested in the logic-low state). Allow the DUT to stabilize at the test temperature.

- 3) Put the pin under test in logic-high state. Measure nominal I<sub>supply</sub> (I<sub>nom</sub>) for each V<sub>supply</sub> pin (or pin group, see Table 2). Then, apply the positive current trigger (per Table 2 for a duration as specified in Table 3) to the pin under test.

- 4) After the trigger source has been removed, return the pin under test to the level it was in before the application of the trigger pulse, and measure the  $I_{supply}$  for each  $V_{supply}$  pin (or pin group). If any  $I_{supply}$  is greater than or equal to the failure criteria specified in Table 2, latch-up has occurred and power must be removed from the DUT. If latch-up has occurred, stop the test; the DUT has failed latch-up testing. Using a new part, return to step 1 and continue testing.

- 5) If latch-up has not occurred, after the necessary cool-down time (see Table 3), repeat steps 3 and 4 for all pins to be tested (noting the exceptions stated in step 2).

- 6) Repeat steps 2 through 5 with all input pins, including bi-directional I/O pins in an input state or high impedance state, not used for preconditioning the I/O pins tied to the minimum logic-low level specified in the device specification.

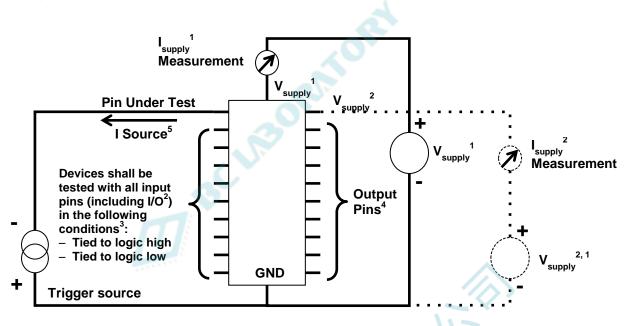

- 7) Bias the DUT as indicated in Figure 5 with all input pins, including bi-directional I/O pins in an input state or high impedance state, not used for preconditioning the I/O pins shall be tied to the maximum logic-high level specified in the device specification (noting the exceptions stated in step 2).

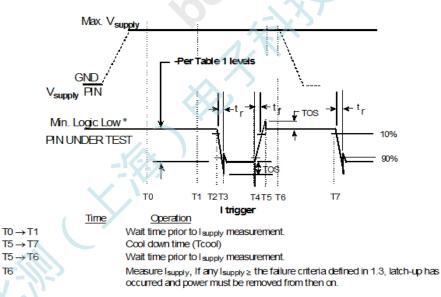

- 8) Put the pin under test in logic-low state. Measure nominal I<sub>supply</sub> (I<sub>nom</sub>) for each V<sub>supply</sub> pin (or pin group, see Table 2). Then, apply the negative current trigger source below ground (per Table 2 for a duration as specified in Table 3) to the pin under test.

- 9) After the trigger source has been removed, return the pin under test to the level it was in before the application of the trigger pulse and measure the  $I_{supply}$  for each  $V_{supply}$  pin (or pin group). If any  $I_{supply}$  is greater than or equal to the failure criteria specified in Table 2, latch-up has occurred and power must be removed from the DUT. If latch-up has occurred, stop the test; the DUT has failed latch-up testing. Using a new part, return to step 1 and continue testing.

- 10) If latch-up has not occurred, after the necessary cool-down time (see Table 3), repeat steps 8 and 9 for all pins to be tested.

- 11) Repeat steps 8 through 10 with all input pins, including bi-directional I/O pins in an input state or high impedance state, not used for preconditioning the I/O pins tied to the minimum logic-low level specified in the device specification (noting the exceptions stated in step 2).

I-test in 4.2.1 does not require the removal of power-supply voltage between stresses, i.e., cool-down time. Users should evaluate the risk of leaving the power-supply on.

\* Max. logic high and min. logic low shall be per the device specification. When logic levels are used with respect to a non-digital device, it means the maximum high or minimum low voltage that can be supplied to the pin per the device.

NOTE The pin under test shall be set to logic high before positive current trigger. It is permissible to start positive current trigger from logic low, but failing results should be confirmed from the logic high state.

Figure 2 — Test waveform for positive I-test

\* Max. logic high and min. logic low shall be per the device specification. When logic levels are used with respect to a non-digital device, it means the maximum high or minimum low voltage that can be supplied to the pin per the device.

NOTE The pin under test shall be set to logic low before negative current trigger. It is permissible to start negative current trigger from logic high, but failing results should be confirmed from the logic low state.

#### Figure 3 — Test waveform for negative I-test

| Table 3 — Timing specification for I-test |                                                             |                                                      |                  |              |  |  |