For Electrostatic Discharge Sensitivity Testing

Human Body Model (HBM) -Component Level

> EOS/ESD Association, Inc. 7900 Turin Road, Bldg. 3 Rome, NY 13440

JEDEC Solid State Technology Association 3103 North 10th Street Arlington, VA 22201

An American National Standard Approved May 12, 2017

BC INSORMIORA BC INSORMIORA Walls And State of the State of ESDA/JEDEC Joint Standard for Electrostatic Discharge Sensitivity Testing -

Human Body Model (HBM) - Component Level

Approved December 8, 2016 EOS/ESD Association, Inc. & JEDEC Solid State Technology Association

## CAUTION NOTICE

EOS/ESD Association, Inc. (ESDA) standards and publications are designed to serve the public interest by eliminating misunderstandings between manufacturers and purchasers, facilitating the interchangeability and improvement of products and assisting the purchaser in selecting and obtaining the proper product for his particular needs. The existence of such standards and publications shall not in any respect preclude any member or non-member of the Association from manufacturing or selling products not conforming to such standards and publications. Nor shall the fact that a standard or publication is published by the Association preclude its voluntary use by non-members of the Association whether the document is to be used either domestically or internationally. Recommended standards and publications are adopted by the ESDA in accordance with the ANSI Patent policy.

Interpretation of ESDA Standards: The interpretation of standards in-so-far as it may relate to a specific product or manufacturer is a proper matter for the individual company concerned and cannot be undertaken by any person acting for the ESDA. The ESDA Standards Chairman may make comments limited to an explanation or clarification of the technical language or provisions in a standard, but not related to its application to specific products and manufacturers. No other person is authorized to comment on behalf of the ESDA on any ESDA Standard.

## DISCLAIMER OF WARRANTIES

THE CONTENTS OF ESDA'S STANDARDS AND PUBLICATIONS ARE PROVIDED "AS-IS," AND ESDA MAKES NO REPRESENTATIONS OR WARRANTIES, EXPRESSED OR IMPLIED, OF ANY KIND WITH RESPECT TO SUCH CONTENTS. ESDA DISCLAIMS ALL REPRESENTATIONS AND WARRANTIES, INCLUDING WITHOUT LIMITATION, WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR USE, TITLE AND NON-INFRINGEMENT.

## DISCLAIMER OF GUARANTY

ESDA STANDARDS AND PUBLICATIONS ARE CONSIDERED TECHNICALLY SOUND AT THE TIME THEY ARE APPROVED FOR PUBLICATION. THEY ARE NOT A SUBSTITUTE FOR A PRODUCT SELLER'S OR USER'S OWN JUDGEMENT WITH RESPECT TO ANY PARTICULAR PRODUCT DISCUSSED, AND ESDA DOES NOT UNDERTAKE TO GUARANTEE THE PERFORMANCE OF ANY INDIVIDUAL MANUFACTURERS' PRODUCTS BY VIRTUE OF SUCH STANDARDS OR PUBLICATIONS. THUS, ESDA EXPRESSLY DISLAIMS ANY RESPONSIBILITY FOR DAMAGES ARISING FROM THE USE, APPLICATION, OR RELIANCE BY OTHERS ON THE INFORMATION CONTAINED IN THESE STANDARDS OR PUBLICATIONS.

## LIMITATION ON ESDA'S LIABILITY

NEITHER ESDA, NOR ITS MEMBERS, OFFICERS, EMPLOYEES OR OTHER REPRESENTATIVES WILL BE LIABLE FOR DAMAGES ARISING OUT OF, OR IN CONNECTION WITH, THE USE OR MISUSE OF ESDA STANDARDS OR PUBLICATIONS, EVEN IF ADVISED OF THE POSSIBILITY THEREOF. THIS IS A COMPREHENSIVE LIMITATION OF LIABILITY THAT APPLIES TO ALL DAMAGES OF ANY KIND, INCLUDING WITHOUT LIMITATION, LOSS OF DATA, INCOME OR PROFIT, LOSS OF OR DAMAGE TO PROPERTY AND CLAIMS OF THIRD PARTIES.

Published by:

EOS/ESD Association, Inc. 7900 Turin Road, Bldg. 3 Rome, NY 13440

JEDEC Solid State Technology Association 3103 North 10th Street Arlington, VA 22201

Copyright © 2017 by EOS/ESD Association, Inc. and JEDEC Solid State Technology Association All rights reserved

No part of this publication may be reproduced in any form, in an electronic retrieval system or otherwise, without the prior written permission of the publisher.

Printed in the United States of America

ISBN: 1-58537-294-3

(This foreword is not part of ESDA/JEDEC Joint Standard ANSI/ESDA/JEDEC JS-001-2017)

#### **FOREWORD**

This joint standard was developed under the guidance of the JEDEC JC-14.1 committee on Reliability Test Methods for Packaged Devices and the ESDA Standards Committee. The content was developed by a joint working group composed of members of the JEDEC ESD Task Group and ESDA Working Group 5.1 (Human Body Model). The standard is intended to replace the human body model ESD standard ANSI/ESDA/JEDEC JS-001-2014.

This revision (2017) introduces a new test level at 50 volts and a new classification. These items have been added to address the increasing number of devices with ESD withstand thresholds in the 50 volt region and below. Technical specifications and guidelines for use of attenuators in making discharge current measurements were added. Attenuators are not recommended for the 50- and 125-volt levels since the expected currents are quite low.

Another change added to this revision is an informative Annex (H) which contains some suggested methods for finding "failure windows", voltage ranges where the device may fail even though it passes at higher levels. While these failure windows are rare, these methods were added so that an accepted approach could be used to demonstrate whether the windows exist in a given case.

The section on safe ESD handling was modified to include citations of the most commonly used ESD control standards. "Threshold" was added to the ESD withstand voltage definition to be consistent with terminology used in the body of the standard. Various typographical errors were also fixed.

This standard is maintained and revised as a joint standard through a Memorandum of Understanding between JEDEC and ESDA. This standard is a living document and revisions and updates will be made on a routine basis driven by the needs of the electronic industry.

For Technical Information Contact: JEDEC Solid State Technology Association 3103 North 10th Street, Suite 204 South Arlington, VA 22201-2107 Phone (703) 907-7559 Fax (703) 907-7583 www.jedec.org

EOS/ESD Association, Inc. 7900 Turin Road, Bldg. 3 Rome, NY 13440 Phone (315) 339-6937 www.esda.org This document was originally designated ANSI/ESDA/JEDEC JS-001-2010 and approved on January 13, 2010. ANSI/ESDA/JEDEC JS-001-2011 was a revision of ANSI/ESDA/JEDEC JS-001-2010 and was approved on March 4, 2011. ANSI/ESDA/JEDEC JS-001-2012 was a revision of ANSI/ESDA/JEDEC JS-001-2011 and was approved on November 16, 2011. ANSI/ESDA/JEDEC JS-001-2014 was a revision of ANSI/ESDA/JEDEC JS-001-2012 and was approved on January 13, 2014. ANSI/ESDA/JEDEC JS-001-2017 is a limited revision of ANSI/ESDA/JEDEC JS-001-2014 and was approved on December 8, 2016. ANSI/ESDA/JEDEC JS-001-2017 was prepared by the ESDA 5.1 Device Testing (HBM) Subcommittee and the JEDEC JC14.1 ESD Task Group. At the time ANSI/ESDA/JEDEC JS-001-2017 was prepared, the Joint HBM Subcommittee had the following members:

| Scott Ward, | Co-Chair |

|-------------|----------|

| Texas Inst  | ruments  |

Robert Ashton

ON Semiconductor

Lorenzo Cerati STMicroelectronics

Barry Fernelius MEFAS, Inc.

Vaughn Gross Green Mountain ESD Labs, LLC

> Marty Johnson Texas Instruments

Timothy Maloney CAI

Paul Ngan NXP Semiconductors

Bill Reynolds GLOBALFOUNDRIES

> Mirko Scholz IMEC

Michael Stevens NXP Semiconductors Andrea Boroni STMicroelectronics

Marcel Dekker MASER Engineering

Reinhold Gaertner Infineon Technologies

Evan Grund Grund Technical Solutions

Chris Jones Semtech Corporation

Thomas Meuse

Thermo Fisher Scientific

Nathaniel Peachey Qorvo

Alan Righter Analog Devices

Theo Smedes

NXP Semiconductors

Teruo Suzuki Socionext Terry Welsher, Co-Chair Dangelmayer Associates

> Brett Carn Intel Corporation

David Eppes Advanced Micro Devices

> Horst Gieser Fraunhofer EMFT

Leo G. Henry ESD/TLP Consultants, LLC

Nicholas Lycoudes NXP Semiconductors

Josh Morris Intel Corporation

> Paul Phillips Phasix ESD

Masanori Sawada Hanwa Electronic Ind. Co., Ltd

Wolfgang Stadler Intel Mobile Communications

Steven H. Voldman Dr. Steven H. Voldman, LLC The following individuals contributed to the development of ANSI/ESDA/JEDEC JS-001-2014, ANSI/ESDA/JEDEC JS-001-2012, ANSI/ESDA/JEDEC JS-001-2011, and ANSI/ESDA/JEDEC JS-001-2010.

| Timothy Archer                   | Robert Ashton                                        | Andrea Boroni                                       |

|----------------------------------|------------------------------------------------------|-----------------------------------------------------|

| STMicroelectronics               | ON Semiconductor                                     | STMicroelectronics                                  |

| Lorenzo Cerati                   | Mike Chaine                                          | Marcel Dekker                                       |

| STMicroelectronics               | Micron Technology                                    | MASER Engineering                                   |

| Marti Farris                     | Barry Fernelius                                      | Reinhold Gaertner                                   |

| Intel Corporation                | MEFAS, Inc.                                          | Infineon Technologies                               |

| Horst Gieser<br>Fraunhofer EMFT  | Vaughn Gross<br>Green Mountain ESD Labs,<br>LLC      | Evan Grund<br>Grund Technical Solutions             |

| Leo G. Henry                     | Michael Hopkins                                      | Larry Johnson                                       |

| ESD/TLP Consultants, LLC         | Amber Precision Instruments                          | LSI Corporation                                     |

| Marty Johnson                    | Chris Jones                                          | Bill Kwong                                          |

| National Semiconductor           | Semtech Corporation                                  | Altera                                              |

| Leo Luquette                     | Nicholas Lycoudes                                    | Timothy Maloney                                     |

| Cypress Semiconductor            | Freescale Semiconductor                              | Intel Corporation                                   |

| Thomas Meuse                     | Douglas Miller                                       | Kyungjin Min                                        |

| Thermo Fisher Scientific         | Sandia National Laboratories                         | Amber Precision Instruments                         |

| Kathleen Muhonen                 | Ravindra Narayan                                     | Paul Ngan                                           |

| RF Micro Devices                 | LSI Logic Corporation                                | NXP Semiconductors                                  |

| Nathaniel Peachey                | Paul Phillips                                        | Bill Reynolds                                       |

| RF Micro Devices                 | Phasix ESD                                           | IBM                                                 |

| Alan Righter<br>Analog Devices   | Masanori Sawada<br>Hanwa Electronic Ind. Co.,<br>Ltd | Mirko Scholz<br>IMEC                                |

| Theo Smedes<br>NXP Semiconductor | Wolfgang Stadler<br>Intel Mobile Communications      | Michael Stevens<br>Freescale Semiconductor,<br>Inc. |

|                                  |                                                      |                                                     |

Scott Ward

**Texas Instruments**

Steven H. Voldman

Dr. Steven H. Voldman, LLC

Terry Welsher

**Dangelmayer Associates**

## TABLE OF CONTENTS

| 1.0 | SCOPE AND PURPOSE                                            | 1  |

|-----|--------------------------------------------------------------|----|

|     | 1.1 Scope                                                    | 1  |

|     | 1.2 Purpose                                                  | 1  |

|     | 1.2.1 Existing Data                                          | 1  |

| 2 0 | REFERENCES                                                   |    |

| 2.0 |                                                              |    |

| _   | 2.1 OTHER DOCUMENTS                                          |    |

| 3.0 | DEFINITIONS                                                  | 1  |

| 4.0 | APPARATUS AND REQUIRED EQUIPMENT                             | 4  |

| 4   | 1.1 WAVEFORM VERIFICATION EQUIPMENT                          | 4  |

|     | 4.1.1 Oscilloscope                                           |    |

|     | 4.1.2 Current Transducer (Inductive Current Probe)           |    |

|     | 4.1.3 Evaluation Loads                                       |    |

|     | 4.1.4 Attenuator                                             | 5  |

| 4   | 1.2 HUMAN BODY MODEL SIMULATOR                               |    |

|     | 4.2.1 HBM Test Equipment Parasitic Properties                | 6  |

| 5.0 | STRESS TEST EQUIPMENT QUALIFICATION AND ROUTINE VERIFICATION | 6  |

| į   | 5.1 OVERVIEW OF REQUIRED HBM TESTER EVALUATIONS              | 6  |

| į   | 5.2 MEASUREMENT PROCEDURES                                   |    |

|     | 5.2.1 Reference Pin Pair Determination                       |    |

|     | 5.2.2 Waveform Capture with Current Probe                    |    |

|     | 5.2.3 Determination of Waveform Parameters                   |    |

|     | 5.2.4 High-Voltage Discharge Path Test                       | 9  |

| į   | 5.3 HBM TESTER QUALIFICATION                                 | 9  |

|     | 5.3.1 HBM Tester Qualification Procedure                     | 9  |

| į   | 5.4 TEST FIXTURE BOARD QUALIFICATION FOR SOCKETED TESTERS    | 10 |

| Ę   | 5.5 ROUTINE WAVEFORM CHECK REQUIREMENTS                      | 11 |

|     | 5.5.1 Standard Routine Waveform Check Description            | 11 |

|     | 5.5.2 Alternate Routine Waveform Capture Procedure           | 12 |

| ţ   | 5.6 High-Voltage Discharge Path Check                        | 12 |

|     | 5.6.1 Relay Testers                                          | 12 |

|     | 5.6.2 Non-Relay Testers                                      | 13 |

| Ę   | 5.7 TESTER WAVEFORM RECORDS                                  | 13 |

|     | 5.7.1 Tester and Test Fixture Board Qualification Records    | 13 |

|     | 5.7.2 Periodic Waveform Check Records                        | 13 |

| į   | 5.8 SAFETY                                                   | 13 |

|     | 5.8.1 Initial Set-Up                                         | 13 |

|     | 5.8.2 Training                                               | 13 |

|     | 5.8.3 Personnel Safety                                       | 13 |

| 6.0 CLASSIFICATION PROCEDURE                                                  | 13             |

|-------------------------------------------------------------------------------|----------------|

| 6.1 PARAMETRIC AND FUNCTIONAL TESTING                                         | 13             |

| 6.1.1 Handling Components                                                     | 14             |

| 6.2 DEVICE STRESSING                                                          |                |

| 6.3 PIN CATEGORIZATION                                                        | 14             |

| 6.3.1 No-Connect Pins                                                         | 15             |

| 6.3.2 Supply Pins                                                             | 15             |

| 6.3.3 Non-Supply Pins                                                         |                |

| 6.4 PIN GROUPINGS                                                             |                |

| 6.4.1 Supply Pin Groups                                                       | 16             |

| 6.4.2 Shorted Non-Supply Pin Groups                                           | 16             |

| 6.5 PIN STRESS COMBINATIONS                                                   | 17             |

| 6.5.1 Non-Supply and Supply to Supply Combinations (1, 2,N)                   | 18             |

| 6.5.2 Non-Supply to Non-Supply Combinations                                   | 19             |

| 6.6 HBM Stressing with a Low-Parasitic Simulator                              | 20             |

| 6.6.1 Low-Parasitic HBM Simulator                                             | 20             |

| 6.6.2 Requirements for Low Parasitics                                         | 20             |

| 6.7 Testing After Stressing                                                   | 20             |

| 7.0 FAILURE CRITERIA                                                          | 20             |

|                                                                               |                |

| ANNEXES                                                                       |                |

| Annex A (Informative) - HBM Test Method Flow Chart                            | 22             |

| Annex B (Informative) - HBM Test Equipment Parasitic Properties               |                |

| Annex C (Informative) - Example of Testing a Product Using Table 2A, 2B, or 2 | 2A with a Two- |

| Pin HBM Tester                                                                |                |

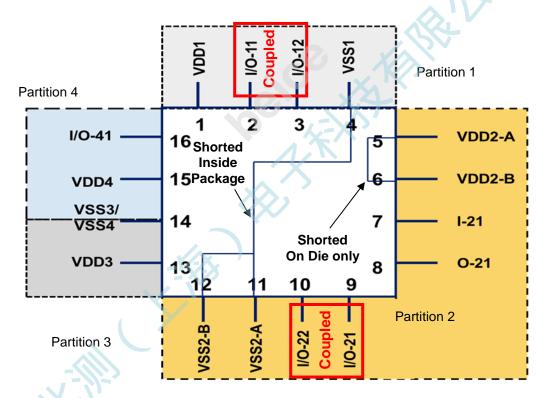

| Annex D (Informative) - Examples of Coupled Non-Supply Pin Pairs              | 36             |

| Annex E (Informative) - Bibliography                                          | 37             |

| Annex F (Normative) - Alternative Table for Table 2B                          | 38             |

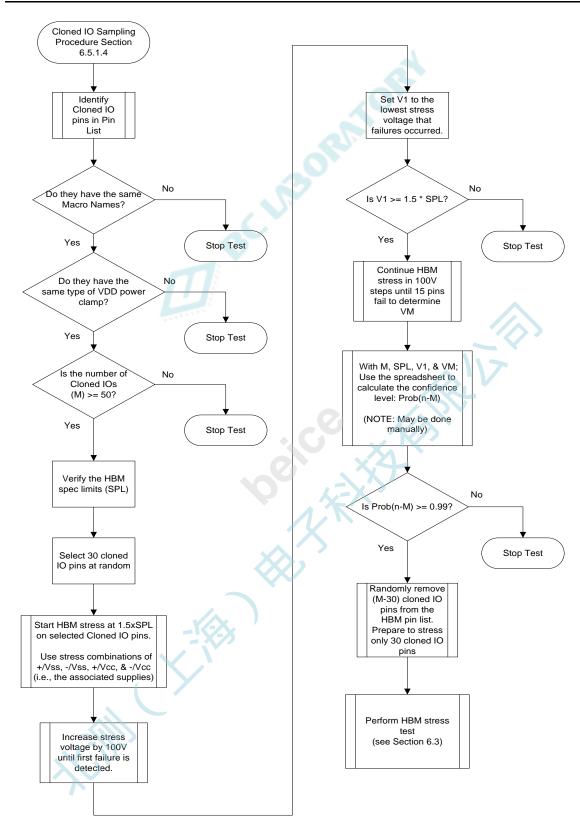

| Annex G (Normative) - Cloned Non-Supply (IO) Pin Sampling Test Method         | 39             |

| Annex H (Informative) - Failure Window Detection Testing Methods              | 45             |

| Annex I (Informative) - ANSI/ESDA/JEDEC JS-001 Revision History               | 46             |

## ANSI/ESDA/JEDEC JS-001-2017

| FIGURES                                                                                 |    |

|-----------------------------------------------------------------------------------------|----|

| Figure 1: Simplified HBM Simulator Circuit with Loads                                   | 5  |

| Figure 2A: Current Waveform through a Shorting Wire (lpsmax)                            | 7  |

| Figure 2B: Current Waveform through a Shorting Wire (t <sub>d</sub> )                   |    |

| Figure 3: Current Waveform through a 500-ohm Resistor                                   |    |

| Figure 4: Peak Current Short-Circuit Ringing Waveform                                   |    |

| Figure 5: Diagram of Trailing Pulse Measurement Setup                                   |    |

| Figure 6: Positive Stress at 4000 Volts                                                 | 26 |

| Figure 7: Negative Stress at 4000 Volts                                                 | 26 |

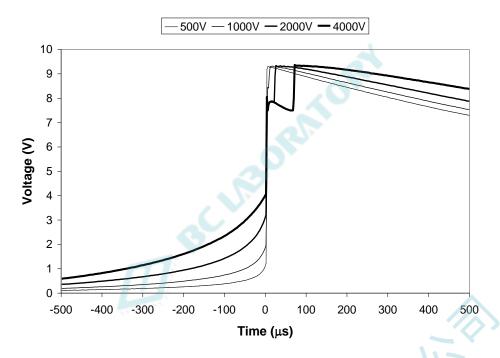

| Figure 8: Illustrates Measuring Voltage before HBM Pulse with a Zener Diode or a Device | 27 |

| Figure 9: Example of Voltage Rise before the HBM Current Pulse across a 9.4 Volt Zener  |    |

| Diode                                                                                   | 28 |

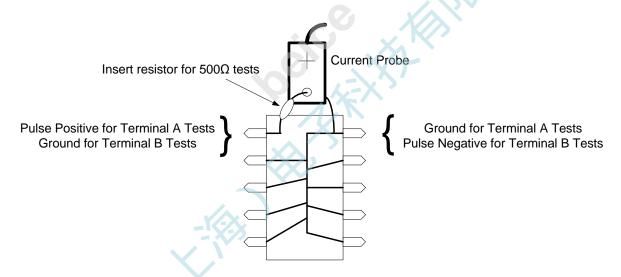

| Figure 10: Diagram of a 10-Pin Shorting Test Device Showing Current Probe               | 29 |

| Figure 11: Example to Demonstrate the Idea of the Partitioned Test                      | 30 |

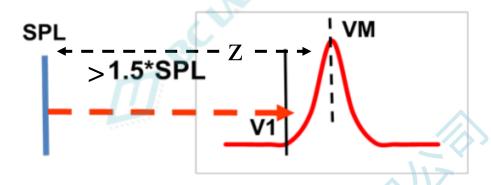

| Figure 12: SPL, V1, VM, and z with the Bell Shape Distribution Pin Failure Curve        |    |

| Figure 13: IO Sampling Test Method Flow Chart                                           |    |

|                                                                                         |    |

|                                                                                         |    |

| TABLES                                                                                  |    |

| Table 1: Waveform Specification                                                         | 11 |

| Table 2A: Required Pin Combination Sets                                                 | 17 |

| Table 2B: Legacy Pin Combination Sets                                                   | 18 |

| Table 3: HBM ESD Component Classification Levels                                        | 21 |

|                                                                                         |    |

ESDA/JEDEC Joint Standard for Electrostatic Discharge Sensitivity Testing – Human Body Model (HBM) – Component Level

#### 1.0 SCOPE AND PURPOSE

#### 1.1 Scope

This standard establishes the procedure for testing, evaluating, and classifying components and microcircuits according to their susceptibility (sensitivity) to damage or degradation by exposure to a defined human body model (HBM) electrostatic discharge (ESD).

## 1.2 Purpose

The purpose (objective) of this standard is to establish a test method that will replicate HBM failures and provide reliable, repeatable HBM ESD test results from tester to tester, regardless of component type. Repeatable data will allow accurate classifications and comparisons of HBM ESD sensitivity levels.

## 1.2.1 Existing Data

Data previously generated with testers meeting all waveform criteria of ANSI/ESDA/JEDEC JS-001-2010 and subsequent versions, ANSI/ESD STM5.1-2007, or JESD22-A114F shall be considered valid test data.

#### 2.0 REFERENCES

ESD ADV1.0, ESD Association's Glossary of Terms1

JESD99, JEDEC Standard - Terms, Definitions, and Letter Symbols for Microelectronic Devices<sup>2</sup>

#### 2.1 Other Documents

ANSI/ESD STM5.1-2007, ESD Association Standard Test Method for Electrostatic Discharge Sensitivity Testing - Human Body Model (HBM) Component Level<sup>1</sup>

JESD22 – A114F, December 2008, Electrostatic Discharge (ESD) Sensitivity Testing Human Body Model (HBM)<sup>2</sup>

#### 3.0 DEFINITIONS

The terms used in the body of this document are in accordance with the definitions found in ESD ADV1.0, ESD Association's Glossary of Terms and JESD99 JEDEC Standard –Terms, Definitions, and Letter Symbols for Microelectronic Devices. Terms separated by a semicolon (;) are considered to be synonyms. In this document the term "pin" is used to represent any device pin, land, bump, ball, or die pad.

**above-passivation layer (APL)**. A low-impedance metal plane, built on the surface of a die above the passivation layer that connects a group of bumps or pins (typically power or ground).

NOTE: This structure is sometimes referred to as a redistribution layer (RDL). There may be multiple APLs (sometimes referred to as islands) for a power or ground group.

**associated non-supply pin.** A non-supply pin (typically an input, output or I/O pin) is associated with a supply pin group if either:

<sup>&</sup>lt;sup>1</sup> EOS/ESD Association, Inc., 7900 Turin Road, Bldg. 3, Rome, NY 13440; Ph: 315-339-6937; www.esda.org

<sup>&</sup>lt;sup>2</sup> JEDEC, 3103 North 10<sup>th</sup> Street, Arlington, VA 22201; Ph: 703-907-7534; FAX: 703-907-7534; www.jedec.org

- the current from the supply pin group (i.e., VDDIO) is required for the function of the electrical circuit(s) (I/O driver) that connect (high/low impedance) to that non-supply pin; or

- a parasitic path exists between non-supply and supply pin group (e.g., open-drain type non-supply pin to a VCC supply pin group that connects to a nearby N-well guard ring).

**cloned non-supply (IO) pin.** Any of a set of input, output, or bidirectional pins using the same IO cell and electrical schematic and sharing the same associated supply pin group(s) including ESD power clamp(s).

component. An item such as a resistor, diode, transistor, integrated circuit or hybrid circuit.

NOTE: A component may also be referred to as a device.

**component failure.** A condition in which a tested component does not meet one or more specified static or dynamic data sheet parameters.

**coupled non-supply pin pair.** Two pins, such as differential amplifier inputs, or low-voltage differential signaling (LVDS) pins, that have between them an intended direct current path, such as a pass gate or resistor.

NOTE: These pairs include analog and digital differential pairs and other special function pairs (e.g., D+/D-, XTALin/XTALout, RFin/RFout, TxP/TxN, RxP/RxN, CCP\_DP/CCN\_DN etc.).

**data sheet parameter.** Any of the static and dynamic component performance data supplied by the component manufacturer or supplier in a data sheet or other product specification.

dynamic parameter. A parameter measured with the component in an operating condition.

NOTE: These may include, but are not limited to full functionality, output rise and fall times under a specified load condition, and dynamic current consumption.

**ESD withstand voltage; withstand threshold.** The highest voltage level that does not cause device failure with the device passing all tests performed at lower voltages.

NOTE: See note under "failure window" definition.

**exposed pad.** An exposed metal plate on an IC package, connected to the silicon substrate and acting as a heat sink.

NOTE 1: This metal plate may or may not be electrically connected to the die.

NOTE 2: The exposed pad may be categorized as either supply, non-supply or no-connect.

**failure window.** An intermediate range of stress conditions that can induce failure in a particular device type while the device type can pass some stress conditions both higher and lower than this range.

NOTE: For example, a component with a failure window may pass a 500-volt test, fail a 1000-volt test and pass a 2000-volt test. Hence, the failure window of the device is between 500 volts and 2000 volts. The withstand voltage of this device is 500 volts.

**feedthrough.** A direct or indirect (via a series resistor) connection from a pad cell layout that can allow additional elements, not included in the pad cell, to make electrical connections to the bond pad. (See Annex G.)

NOTE: This is not to be confused with the term feedthrough used in Section 5.0 which refers to test boards.

**HBM ESD tester; HBM simulator.** Equipment that applies a human body model (HBM) ESD to a component.

NOTE: This equipment is also referred to as "tester" in this standard.

**human body model (HBM) ESD.** An electrostatic discharge (ESD) event meeting the waveform criteria specified in this standard, approximating the discharge from the fingertip of a typical human being to a grounded device.

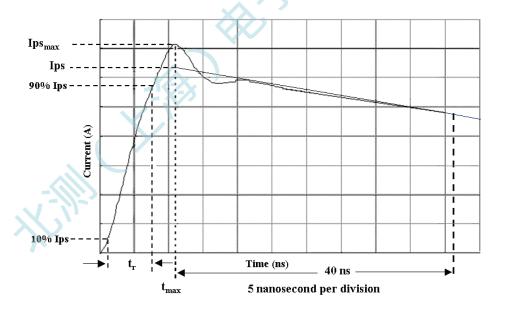

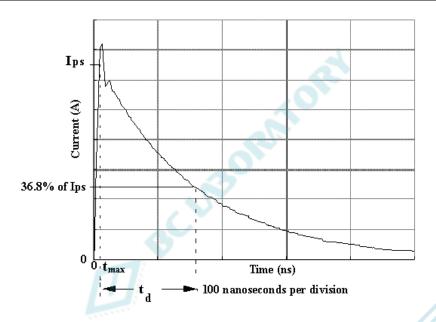

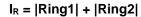

**Ips (peak current value).** The current value determined by linear extrapolation of the exponential current decay curve back to the time ( $t_{max}$ ) when the current actually peaked ( $lps_{max}$ ).

NOTE: The linear extrapolation should be based on the current waveform data over a 40-nanosecond period beginning at  $t_{max}$ . (See Figure 2A.)

**lps**<sub>max</sub> (peak current maximum value). The highest current value measured.

NOTE: This value includes the overshoot or ringing components due to internal test simulator RLC parasitics. (See Figure 2A.)

**no-connect pin.** A package interconnect (pin, bump, or ball) that is not electrically connected to a die.

NOTE: In practice, there are some pins that are labeled as "no-connect", but that are actually connected to the die and, therefore, should not be classified as a no-connect pins for the purpose of ESD testing.

**non-socketed tester.** An HBM simulator that makes contact to the device under test (DUT) pins (or balls, lands, bumps, or die pads) with test probes rather than placing the DUT in a socket.

non-supply pin. A pin that is not categorized as a supply pin or a no-connect.

NOTE: Non-supply pins include pins such as input, output, offset adjusts, compensation, clocks, controls, address, data, Vref pins and VPP pins on EPROM memory. Most non-supply pins transmit or receive information such as digital or analog signals, timing, clock signals, and voltage or current reference levels.

**package plane.** A low-impedance metal layer built into an IC package connecting a group of bumps or pins (typically power or ground). There may be multiple package planes (sometimes referred to as islands) for each power and ground group.

**pre-pulse voltage.** A voltage occurring at the device under test (DUT) just prior to the generation of the HBM current pulse. (See Annex B.2.)

**pulse generation circuit.** The circuit network that produces a human body discharge current waveform.

NOTE: The circuit network includes a pulse generator with its test equipment internal path up to the contact pad of the test fixture.

NOTE: This circuit is also referred to as a dual-polarity pulse source.

**ringing.** A high-frequency oscillation superimposed on a waveform.

**shorted non-supply pin.** Any non-supply pin (typically an input, output or I/O pin) that is metallically connected (typically < 3 ohm) on the chip or within the package to another non-supply pin (or set of non-supply pins).

**socketed tester.** A simulator that makes contact to DUT pins (or balls, lands, bumps, or die pads) using a DUT socket mounted on a test fixture board.

**specification limit (SPL).** The HBM limit value set by customer requirement or internal target. (See Annex G.)

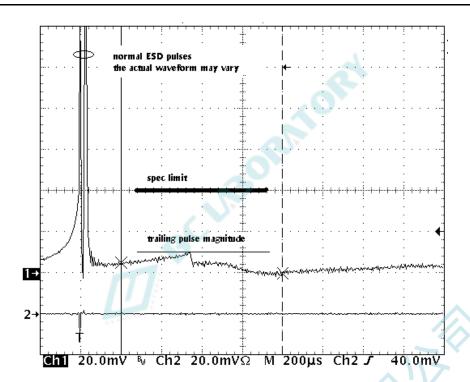

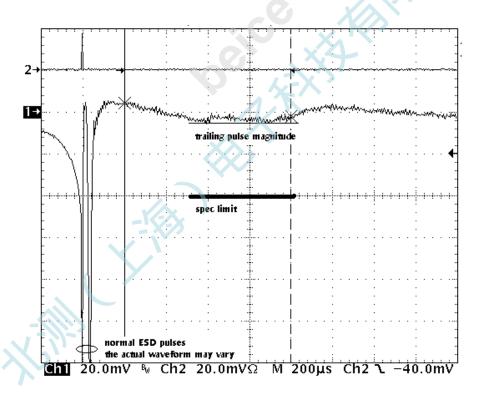

**spurious current pulse.** A small HBM shaped pulse that follows the main current pulse and is typically defined as a percentage of Ips<sub>max</sub>.

**supply pin.** Any device pin that provides operating current to that device.

NOTE: Supply pins typically transmit no information (such as digital or analog signals, timing, clock signals, and voltage or current reference levels). For the purpose of ESD testing, power and ground pins are treated as supply pins.

static parameter. A parameter measured with the component in a non-operating condition.

NOTE: Static parameters may include, but are not limited to, input leakage current, input breakdown voltage, output high and low voltages, output drive current, and supply current.

**step-stress-test hardening.** The process of increasing the ESD withstand threshold by applying stress incrementally from low voltage to higher values.

NOTE: This hardening occurs when a component subjected to increasing ESD voltage step-stresses is able to withstand higher stress levels than when another component expected to have the same threshold is evaluated using no step-stressing.

NOTE: For example: a component may fail at 1000 volts if subjected to a single stress, but fail at 3000 volts if stressed incrementally from 250 volts.

**test fixture board.** A specialized circuit board, with one or more component sockets, that connects the DUT(s) to the HBM simulator.

t<sub>max</sub>. The time when the current is at its maximum value (Ips<sub>max</sub>). (See Figure 2A.)

**trailing current pulse.** A current pulse that occurs after the HBM current pulse has decayed. (See Annex B.1.)

NOTE: A trailing current pulse is a relatively constant current often lasting for hundreds of microseconds.

**two-pin tester.** A low-parasitic HBM simulator that tests DUTs in pin pairs in which floating pins are not connected to the simulator, thereby eliminating DUT-tester interactions from parasitic tester loading of floating pins.

**V1.** The maximum HBM stress voltage step at which all of the selected cloned non-supply pins pass. (See Annex G.)

**V2.** The minimum HBM stress voltage step at which all the selected cloned non-supply pins fail. (See Annex G.)

**VM.** The minimum HBM stress voltage step at which 50% or greater of the selected cloned non-supply pins fail. (See Annex G.)

#### 4.0 APPARATUS AND REQUIRED EQUIPMENT

#### 4.1 Waveform Verification Equipment

All equipment used to evaluate the tester shall be calibrated in accordance with the manufacturer's recommendation. This includes the oscilloscope, current transducer and high-voltage resistor load. Maximum time between calibrations shall be one year. Calibration shall be traceable to national standards, such as the National Institute of Standards and Technology (NIST) in the United States, or comparable international standards.

Equipment capable of verifying the pulse waveforms defined in this standard test method includes, but is not limited to, an oscilloscope, evaluation loads and a current transducer.

#### 4.1.1 Oscilloscope

A digital oscilloscope is recommended but analog oscilloscopes are also permitted. In order to insure accurate current waveform capture, the oscilloscope shall meet the following requirements:

- a. Minimum sensitivity of 100 milliamperes per major division when used in conjunction with the current transducer specified in Section 4.1.2.

- b. Minimum bandwidth of 350 MHz.

- c. For analog scopes, minimum writing rate of one major division per nanosecond.

## 4.1.1.1 Additional Requirements for Digital Oscilloscopes

a. Recommended channels: 2 or more

b. Minimum sampling rate: 1 GS/s

c. Minimum vertical resolution: 8-bit

d. Minimum vertical accuracy: +2.5%

e. Minimum time base accuracy: 0.01%

f. Minimum record length: 10 k points

#### 4.1.2 Current Transducer (Inductive Current Probe)

- Minimum bandwidth of 200 MHz.

- b. Peak pulse capability of 12 amperes.

- c. Rise time of less than 1 nanosecond.

- d. Capable of accepting a solid conductor as specified in Section 4.1.3.

- e. Provides an output voltage per signal current as required in Section 4.1.1. (This is usually between 1 and 5 millivolts per milliampere.)

- f. Low-frequency 3-dB-point below 10 kHz (e.g., Tektronix CT2) for measurement of decay constant t<sub>d</sub> (see Section 5.2.3.1, Table 1, and note below).

NOTE: Results using a current probe with a low-frequency 3-dB-point of 25 kHz (e.g., Tektronix CT1) to measure decay constant  $t_d$  are acceptable if  $t_d$  is found to be between 130 and 165 nanoseconds.

#### 4.1.3 Evaluation Loads

Two evaluation loads are necessary to verify tester functionality:

- a. Load 1: A solid 18-24 AWG (non-US standard wire size 0.25 to 0.75 mm² cross-section) tinned copper shorting wire as short as practicable to span the distance between the two farthest pins in the socket while passing through the current probe or long enough to pass through the current probe and contacted by the probes of a non-socketed tester.

- b. Load 2: 500 ohms,  $\pm$  1%, minimum 4000-volt rating.

#### 4.1.4 Attenuator

A 20.0 dB attenuator with a precision of  $\pm$  0.5 dB, at least 1 GHz bandwidth, and an impedance of 50 ohms  $\pm$  5 ohms.

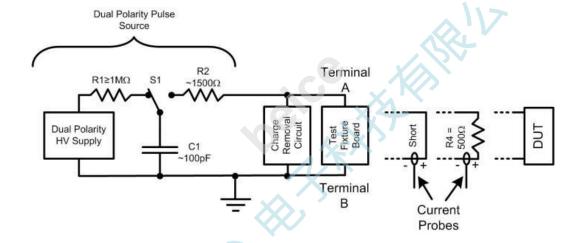

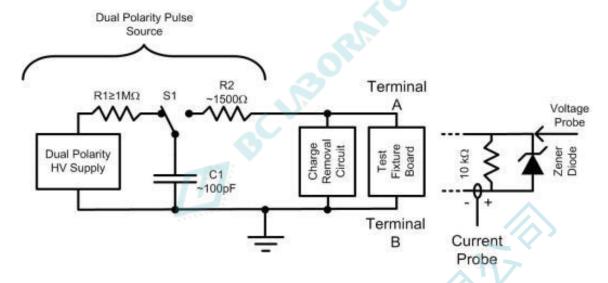

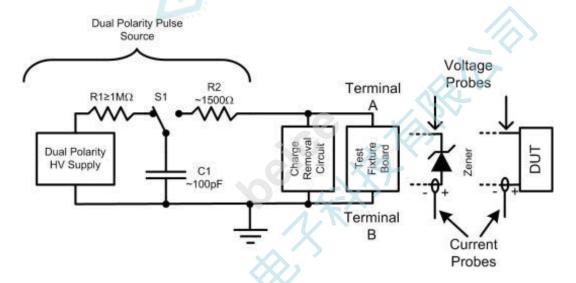

## 4.2 Human Body Model Simulator

A simplified schematic of the HBM simulator or tester is given in Figure 1. The performance of the tester is influenced by parasitic capacitance and inductance. Thus, construction of a tester using this schematic does not guarantee that it will provide the HBM pulse required for this standard. The waveform capture procedures and requirements described in Section 5.0 determine the acceptability of the equipment for use.

Figure 1: Simplified HBM Simulator Circuit with Loads

#### NOTES:

- 1. The current transducers (current probes) are specified in Section 4.1.2.

- 2. The shorting wire (Short) and 500-ohm resistor (R4) are evaluation loads specified in Section 4.1.3.

- Reversal of Terminals A and B to achieve dual polarity performance is not permitted except under conditions described in, Sections 6.5.1.3 and 6.6.

- 4. The charge removal circuit ensures a slow discharge of the device, thus avoiding the possibility of a charged device model discharge. A simple example is a 10-kilohm or larger resistor (possibly in series with a switch) in parallel with the test fixture board. This resistor may also be useful to control parasitic pre-pulse voltages (See Annex B.2).

- The dual polarity pulse source (generator) shall be designed to avoid recharge transients and double pulses.

- Stacking of DUT socket adapters (piggybacking or the insertion of secondary sockets into the main test socket) is allowed only if the secondary socket waveform meets the requirements of this standard defined in Table 1.

- 7. Component values are nominal.

#### 4.2.1 HBM Test Equipment Parasitic Properties

Some HBM simulators have been found to falsely classify HBM sensitivity levels due to parasitic artifacts or uncontrolled voltages unintentionally built into the HBM simulators. Methods for determining if these effects are present and optional mitigation techniques are described in Annex B. Two-pin testers and non-socketed testers may have smaller parasitic capacitances and may reduce the effects of tester parasitics by contacting only the pins being stressed.

#### 5.0 STRESS TEST EQUIPMENT QUALIFICATION AND ROUTINE VERIFICATION

## 5.1 Overview of Required HBM Tester Evaluations

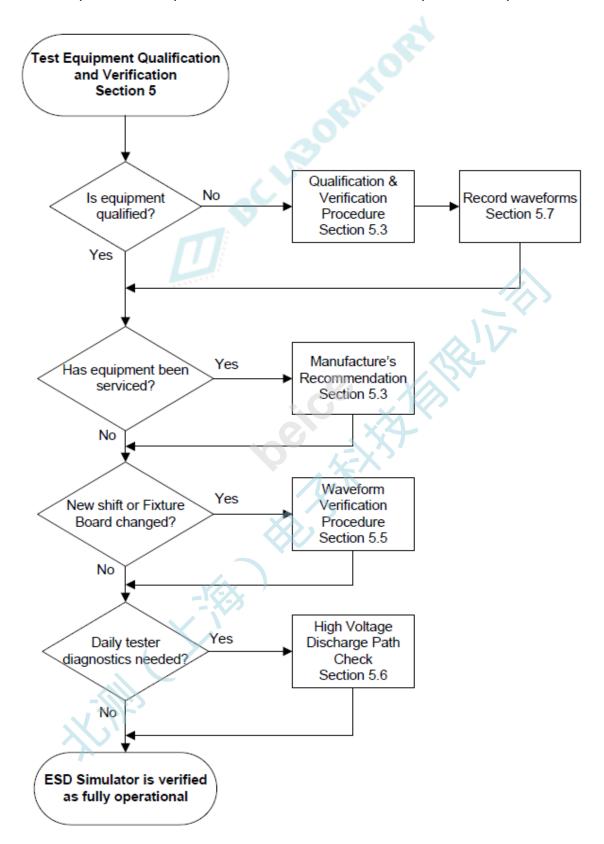

The HBM tester and test fixture boards shall be qualified, re-qualified, and periodically verified as described in this section. A flow chart for this procedure is given in Annex A. The safety precautions described in Section 5.8 should be followed at all times.

#### 5.2 Measurement Procedures

#### 5.2.1 Reference Pin Pair Determination

The two pins of each socket on a test fixture board which make up the reference pin pair are (1) the socket pin with the shortest wiring path of the test fixture to the pulse generation circuit (Terminal B) and (2) the socket pin with the longest wiring path of the test fixture from the pulse generation circuit (Terminal A) to the ESD stress socket, see Figure 1. This information is typically provided by the equipment or test fixture board manufacturer. If more than one pulse generation circuit is connected to a socket then there will be more than one reference pin pair.

It is strongly recommended that on non-positive clamp fixtures, feed through test point pads be added on these paths, to allow connection of either the shorting wire or 500-ohm load resistor during waveform verification measurements. These test points should be added as close as possible to the socket(s), and if the test fixture board uses more than one pulse generator, multiple feed through test points should be added for each pulse generator's longest and shortest paths.

NOTE: A positive clamp test socket is a zero insertion force (ZIF) socket with a clamping mechanism. It allows the shorting wire to be easily clamped into the socket. Examples are dual in-line package (DIP) and pin grid array (PGA) ZIF sockets.

#### 5.2.2 Waveform Capture with Current Probe

To capture a current waveform between two socket pins (usually the reference pin pair), use the shorting wire (Section 4.1.3, Load 1) for the short-circuit measurement or the 500-ohm resistor (Section 4.1.3, Load 2) for the 500-ohm current measurement and the inductive current probe (Section 4.1.2).

NOTE: At high stress voltages, an attenuator (Section 4.1.4) may be necessary to prevent off scale measurements on the oscilloscope and avoid oscilloscope damage. At low stress levels, especially at the 50 and 125 volt levels, an attenuator should not be used when signal levels reach the lower limits of the oscilloscope voltage sensitivity.

#### 5.2.2.1 Short-Circuit Current Waveform

Place the current probe around the shorting wire, as close to Terminal B as practical, observing the polarity as shown in Figure 1. Attach the shorting wire between the pins to be measured, with the current probe as close to Terminal B as practical, observing the polarity as shown in Figure 1. Apply an ESD stress at the voltage and polarity needed to execute the qualification, re-qualification or periodic verification being conducted.

- For positive clamp sockets, insert the shorting wire between the socket pins connected to Terminals A and B and hold in place by closing the clamp.

- b. For non-positive clamp sockets, attach the shorting wire between the socket pins connected to Terminals A and B. If it is not possible to make contact within the socket, connect the shorting wire between the reference pin pair feed through test points, if available.

NOTE: The design of the socket is important as some socket types may include contact springs (coils) in their design. These springs can add more parasitic inductance to the signal path and may affect the HBM waveform. Selecting sockets that minimize the use of springs (coils) is recommended, but if this is not possible, then keeping their length as short as possible is recommended.

c. For non-socketed testers, the shorting wire with the inductive current probe is placed on an insulating surface and the simulator Terminal A and Terminal B probes are placed on the ends of the wires.

#### 5.2.2.2 500-Ohm Load Current Waveform

Place the current probe around the 500-ohm resistor's lead, observing the polarity as shown in Figure 1. Attach the 500-ohm resistor between the pins to be measured with the current probe as close to Terminal B s practical. Apply an ESD stress at the voltage and polarity needed to execute the qualification, re-qualification or periodic verification being conducted.

- a. For socketed testers, follow procedures according to socket type as described in Section 5.2.2.1.

- b. For non-socketed testers, place the test load and current probe on an insulating surface and connect the tester's probes to the ends of the test load.

## 5.2.3 Determination of Waveform Parameters

The captured waveforms are used to determine the parameter values listed in Table 1.

## 5.2.3.1 Short-Circuit Waveform

Typical short-circuit waveforms are shown in Figures 2A, 2B, and 4. The parameters Ips (peak current),  $t_r$  (pulse rise time),  $t_d$  (pulse decay time) and  $l_R$  (ringing) are determined from these waveforms. Ringing may prevent the simple determination of Ips. A graphical technique for determining Ips and  $l_R$  is described in Section 5.2.3.3 and Figure 4.

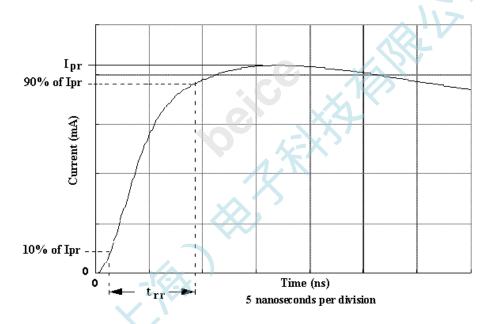

#### 5.2.3.2 500-Ohm Load Waveform

A typical 500-ohm load waveform is shown in Figure 3. The parameters I<sub>pr</sub> (peak current with 500-ohm load) and t<sub>rr</sub> (pulse rise time with 500-ohm load) are determined from this waveform.

Figure 2A: Current Waveform through a Shorting Wire (Ipsmax)

Figure 2B: Current Waveform through a Shorting Wire (t<sub>d</sub>)

Figure 3: Current Waveform through a 500-ohm Resistor

## 5.2.3.3 Graphical Determination of lps and I<sub>R</sub> (See Figure 4)

5.2.3.3.1 A line is drawn (manually or using numerical methods such as least squares) through the HBM ringing waveform from  $t_{max}$  to  $t_{max}$  + 40 ns to interpolate the value of the curve for a more accurate derivation of the peak current value (lps).  $t_{max}$  is the time when  $t_{max}$  occurs (see definition for  $t_{max}$  in Section 3 and Figure 2A).

5.2.3.3.2 The maximum deviation of the measured current above the straight line fit is Ring1. The maximum deviation of the measured current below the straight line fit is Ring2. The maximum ringing current during a short-circuit waveform measurement is defined as:

Figure 4: Peak Current Short-Circuit Ringing Waveform

## 5.2.4 High-Voltage Discharge Path Test

This test is only required for relay-based testers. This test is intended to ensure that the tester high-voltage relays and the grounding relays that connect pulse generator(s) (i.e., Terminal A) and current return paths (i.e., Terminal B) to the DUT are functioning properly. The tester manufacturer should provide a recommended procedure and, if needed, a verification board and software.

#### 5.3 HBM Tester Qualification

HBM ESD tester qualification as described in this section is required in the following situations:

- a. Acceptance testing when the ESD tester is delivered or prior to first use.

- b. Periodic re-qualification in accordance with manufacturer's recommendations. The maximum time between re-qualification tests is one year.

- c. After service or repair that could affect the waveform.

## 5.3.1 HBM Tester Qualification Procedure

5.3.1.1 Test Fixture Board, Socket and Pins for Socketed Testers Only

Use the highest pin count test fixture board with a positive clamp socket for the tester waveform verification or the recommended waveform verification board provided by the manufacturer.

The reference pin pair(s) of the highest pin count socket on the board shall be used for waveform capture. Waveforms from every pulse generating circuit are to be recorded.

Electrical continuity for all pins on the test fixture board shall be verified prior to qualification testing. This can typically be done using the manufacturer's recommended self-test.

## 5.3.1.2 Short-Circuit Waveform Capture

- a. For socketed testers: Configure the test fixture board, shorting wire, and transducer for the short-circuit waveform measurement as described in Section 5.2.2.1.

- For non-socketed testers: Configure the shorting wire and transducer for the short-circuit waveform measurement as described in Section 5.2.2.1(c).

- b. Apply five positive and five negative pulses at each non-optional test voltage in Table 1. Verify that the waveforms meet all parameters specified in Figures 2A, 2B, and 4, and Table 1. Record waveforms at 1000, 2000, and 4000 volts.

- c. If the optional levels (50 V, 125 V and/or 8000 V) are intended to be used, then 5.3.1.2a and 5.3.1.2b shall be completed for those levels.

## 5.3.1.3 500-Ohm Load Waveform Capture

- a. For socketed testers: Configure the test fixture board, resistor, and transducer for the 500-ohm load waveform measurement as described in Section 5.2.2.2.

- For non-socketed testers: Configure the resistor and transducer for the 500-ohm load waveform measurement as described in Section 5.2.2.2(b).

- b. Record waveforms at 1000 and 4000 volts, both positive and negative polarities. Verify that the waveforms meet all parameters specified in Figure 3 and Table 1.

### 5.3.1.4 Spurious Current Pulse Detection

Secondary pulses after the HBM pulses are generated by the discharge relay. Using the shorting wire configuration, initiate a 1000-volt pulse and verify that any pulses after the initial HBM pulse are less than 15% of the amplitude of the main pulse.

NOTE: For analog oscilloscopes, setting the time base to 1 millisecond/division can detect these types of pulses. For digital oscilloscopes, current pulses after the initial current pulse can be observed, but advanced triggering functions such as sequential triggering or delayed triggering may be needed so secondary pulses are not missed due to low sampling rates.

## 5.4 Test Fixture Board Qualification for Socketed Testers

Test fixture boards shall be qualified in a qualified tester prior to initial use or after repair. This procedure is also required when a previously qualified test fixture board is used in a different model HBM simulator from the one in which it was originally qualified. The procedure shall be applied to the reference pin pairs on all sockets of the new test fixture board. If there is not adequate physical access to the socket, follow the guidance of Section 5.2.2.1(b).

- **5.4.1** Configure the test fixture board, shorting wire, and current probe for the short-circuit waveform measurement as described in Section 5.2.2.1 with a qualified tester.

- **5.4.2** Apply at least one positive and one negative 1000-volt pulse. All waveform parameters shall be within the limits specified in Figures 2A, 2B, and 4, and Table 1.

- **5.4.3** Configure the test fixture board, 500-ohm resistor, and transducer for the 500-ohm load waveform measurement as described in Section 5.2.2.2.

**5.4.4** Apply at least one positive and one negative 1000-volt pulse. All waveform parameters shall be within the limits specified in Figure 3 and Table 1.

5.4.5 Repeat for all additional reference pin pairs of all pulse generating circuits and sockets.

**Table 1. Waveform Specification**

| Voltage<br>Level<br>(V) | Ipeak for<br>Short,<br>Ips<br>(A) | lpeak for<br>500 Ω<br>lpr<br>(A) | Rise Time<br>for Short,<br>tr<br>(ns) | Rise Time<br>for 500 Ω<br>trr<br>(ns) | Decay<br>Time for<br>Short,<br>td<br>(ns) | Maximum<br>Ringing<br>Current<br>I <sub>R</sub><br>(A) |

|-------------------------|-----------------------------------|----------------------------------|---------------------------------------|---------------------------------------|-------------------------------------------|--------------------------------------------------------|

| 50<br>(optional)        | 0.027-<br>0.040                   | N/A                              | 2.0-10                                | N/A                                   | 130-170                                   | 15% of lps                                             |

| 125<br>(optional)       | 0.075-<br>0.092                   | N/A                              | 2.0-10                                | N/A                                   | 130-170                                   | 15% of lps                                             |

| 250                     | 0.15-0.18                         | N/A                              | 2.0-10                                | N/A                                   | 130-170                                   | 15% of lps                                             |

| 500                     | 0.30-0.37                         | N/A                              | 2.0-10                                | N/A                                   | 130-170                                   | 15% of lps                                             |

| 1000                    | 0.60-0.7 <b>3</b>                 | 0.37-0.55                        | 2.0-10                                | 5.0-25                                | 130-170                                   | 15% of lps                                             |

| 2000                    | 1.20-1.47                         | N/A                              | 2.0-10                                | N/A                                   | 130-170                                   | 15% of lps                                             |

| 4000                    | 2.40-2.9 <b>3</b>                 | 1.5-2.2                          | 2.0-10                                | 5.0-25                                | 130-170                                   | 15% of lps                                             |

| 8000<br>(optional)      | 4.80-5.8 <b>7</b>                 | N/A                              | 2.0-10                                | N/A                                   | 130-170                                   | 15% of lps                                             |

## 5.5 Routine Waveform Check Requirements

## 5.5.1 Standard Routine Waveform Check Description

Waveforms shall be acquired using the short circuit method (Section 5.2.2.1) on the reference pin pair(s) for each socket. If necessary, the test fixture board being used may be removed and replaced with a positive clamp socket test fixture board to facilitate waveform measurements. For non-socketed testers the procedure of Section 5.2.2.1(c) is used. Stresses shall be applied at positive and negative 1000 volts or the stress level to be tested during the use. The waveforms shall meet the requirements of Figures 2A, 2B, and 4, and Table 1.

#### 5.5.1.1 Waveform Check Frequency

The waveforms shall be verified according to this procedure at least once per shift. If ESD stress testing is performed in consecutive shifts, waveform checks at the end of one shift may also serve as the initial check for the following shift.

Longer periods between waveform checks may be used if no changes in waveforms are observed for several consecutive checks. Simpler waveform checks (Section 5.5.2) may be used with longer period between waveform checks as described in this section. For example, Section 5.5.2 tests may be done daily with tests according to Section 5.5.1 done monthly. The test frequency and method chosen shall be documented. If at any time the waveforms no longer meet the specified limits, all ESD stress test data collected subsequent to the previous satisfactory waveform check shall be marked invalid and shall not be used for classification.

If the tester has multiple pulse generation circuits, then the waveform for each pulse generation circuit shall be verified with a positive clamp socket test fixture board. The recommended time period between verification tests is once per shift. However, a rotational method of verification may be used to ensure all pulse generation circuits are functioning properly. For instance, on day 1, pulse generation circuit 1 would be tested. On day 2, pulse generation circuit 2 would be tested, and on day 3, pulse generation circuit 3 would be tested, until all circuits have been tested, at which time circuit 1 would again be tested. The recommended maximum interval between tests of any one pulse generator is two weeks. However, if a pulse generation circuit fails, then all ESD stress tests subsequent to the previous satisfactory waveform check of that pulse generation circuit shall be marked invalid and shall not be used for classification.

## 5.5.2 Alternate Routine Waveform Capture Procedure

As an alternative to the detailed routine waveform analysis, a quick pass/fail waveform capture process can be instituted for routine verification. This method may be used in combination with Section 5.5.1 as described above.

- 5.5.2.1 Capture a waveform using a shorting wire evaluation load at +1000 volts.

- 5.5.2.2 Measure Ips<sub>max</sub> (without adjustment for ringing) and ensure that it is between 0.60 and 0.73 ampere.

- 5.5.2.3 Repeat at -1000 volts.

- 5.5.2.4 If the tester has multiple pulse sources, choose a pin pair combination from a different pulse source each day, rotating through each pulse source in turn as described in Section 5.5.1.1. If  $Ips_{max}$  is within the values specified for both polarities and the waveforms appear normal, the tester is considered ready to use.

NOTE: This measurement does not take into consideration lps ringing; this may affect the results. If there are any concerns about how the waveforms look, or if the measurements are close to the upper or lower specification limits, a complete waveform analysis (Section 5.3.1) shall be performed.

NOTE: The quick pass/fail test method should be applied only to qualified test fixture boards for qualified ESD simulators. Test fixture boards and ESD simulator shall be qualified together using the test method in Section 5.3.1 before using test method Section 5.5.2.

## 5.6 High-Voltage Discharge Path Check

## 5.6.1 Relay Testers

This test is required for either routine check method (Section 5.5). Test the high-voltage discharge and current return paths and all associated circuitry at the beginning of each day during which ESD stress testing is performed (see Section 5.2.4). The period between self-test diagnostic checks may be extended, providing test data supports the increased interval. If any failure is detected, do not perform device testing with the sockets that are connected to the defective discharge paths. Repair the tester and then verify that the failed pins pass the self-test before resuming testing. Depending on the extent of the repair it may be necessary to perform a complete re-qualification according to Section 5.3.1.

#### 5.6.2 Non-Relay Testers

For testers utilizing mechanical switching instead of relay switching, the connections to pins shall be verified for each pin combination during the test. Making continuity measurements immediately prior to stress pulses or monitoring the HBM pulse current during stress pulse are examples of connection verification methods. This practice replaces the daily high-voltage discharge path verification.

#### 5.7 Tester Waveform Records

#### 5.7.1 Tester and Test Fixture Board Qualification Records

Retain the waveform records until the next re-qualification or for the duration specified by the user's internal record keeping procedures.

#### 5.7.2 Periodic Waveform Check Records

Retain the periodic waveform records at least one year for the duration specified by the user's internal record keeping procedures.

## 5.8 Safety

#### 5.8.1 Initial Set-up

During initial equipment set-up, a safety engineer or applicable safety representative shall inspect the equipment in its operating location to ensure that the equipment is not operated in a combustible (hazardous) environment.

#### 5.8.2 Training

All personnel shall receive system operational training and electrical safety training prior to using the equipment.

#### 5.8.3 Personnel Safety

The procedures and equipment described in this document may expose personnel to hazardous electrical conditions. Users of this document are responsible for selecting equipment that complies with applicable laws, regulatory codes and both external and internal policy. Users are cautioned that this document cannot replace or supersede any requirements for personnel safety.

Ground fault circuit interrupters (GFCI) and other safety protection should be considered wherever personnel might come into contact with electrical sources.

Electrical hazard reduction practices should be exercised and proper grounding instructions for equipment shall be followed.

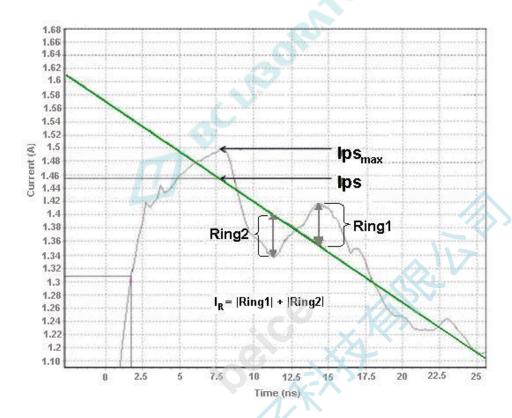

#### 6.0 CLASSIFICATION PROCEDURE

The devices used for classification testing must have completed all normal manufacturing operations. A flow chart for this procedure is given in Annex A. Testing must be performed using an actual device chip. It is not permissible to use a test chip representative of the actual chip or to assign threshold voltages based on data compiled from a design library or via software simulations. ESD classification testing shall be considered destructive to the component, even if no component failure is detected.

NOTE: Test chip in this case means ESD test structure.

#### 6.1 Parametric and Functional Testing

Prior to ESD stressing, parametric and functional testing using conditions required by the applicable part drawing or test specification shall be performed on all devices submitted. Parametric and functional test results shall be within the limits stated in the part drawing for these parameters.

## **6.1.1 Handling Components**

ESD damage prevention procedures shall be used before, during and after HBM and post parametric testing.

NOTE: See the latest revision of ANSI/ESD S20.20, JESD625, or IEC61340-5-1 for guidance.

#### 6.2 Device Stressing

A sample of three devices for each voltage level shall be characterized for the device ESD withstand threshold using the voltage levels shown in Table 1. Finer voltage steps may optionally be used to obtain a more accurate measure of the withstand threshold, and to improve detection of devices exhibiting failure windows. (See Annex H). It is recommended that ESD testing begin at the lowest level in Table 1 for failure window detection but testing may begin at any level. However, if the initial voltage level is higher than the lowest level in Table 1, and the device fails at the initial voltage, testing shall be restarted with three fresh devices at the next lowest level. (E.g., if the initial voltage is 1000 volts and the device fails, restart the test at 500 volts.) The ESD test shall be performed at room temperature.

NOTE: It is recommended to verify continuity between device pins and the socket after inserting devices to be tested. Leakage measurements or curve tracing may be used.

For each voltage level, a sample of three devices shall be stressed using at least 1 positive and at least 1 negative pulse with a minimum of 100 milliseconds between pulses per pin for all pin combinations specified in Table 2. Separate samples may be used for different polarities.

NOTE: References to Table 2 in this section refer to use of either Table 2A or Table 2B.

NOTE: In some ESD simulators, a charge removal circuit is not present. For these simulators, increasing the time between pulses to prevent a charge build-up is one method to reduce the risk for subsequent pin overstress. Alternatively, curve trace leakage tests after each pulse for all pins in the DUT will also remove this excess charge stored in the test fixture board or socket.

Three new components may be used at each voltage level or pin combination if desired. This will eliminate any step-stress hardening effects, and reduce the possibility of early failure due to cumulative stress. In isolated cases it is possible for failure windows to exist below the determined withstand threshold. See Informative Annex H for methods that can be used for failure window testing. It is permitted to further partition each pin combination set in Table 2 and use a separate sample of three devices for each subset within the pin combination set.

It is permitted to partition testing of devices among different testers as long as all testers are qualified (per Section 5.3) and all pin combinations of Table 2 are tested with at least one sample of three devices.

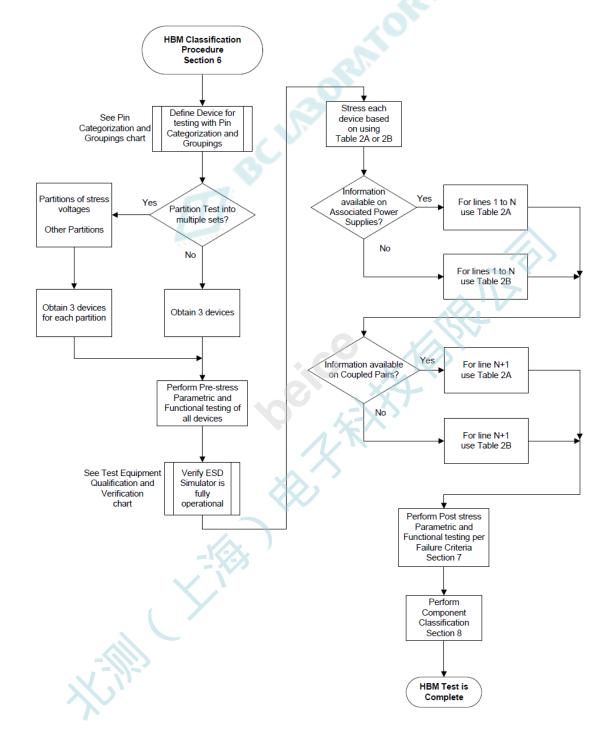

#### 6.3 Pin Categorization

HBM testing is done using pin combinations as described in Tables 2A or 2B. A flow chart for this categorization process is given in Annex A. The purpose of the pin combinations is to test all of the major HBM current paths. Setting up the pin combinations requires knowledge of the device under test. Each pin of the device must be classified as a no connect, supply pin or non-supply pin. These pin categories are defined in Sections 6.3.1 through 6.3.3. Additionally, supply pins must be grouped into supply pin groups as described in Section 6.4.1. With this basic knowledge testing may be done using Table 2B. (Table 2B describes the pin combinations as used in ANSI/ESDA/JEDEC JS-001-2010 and previous JEDEC and ESDA HBM standards.) With additional knowledge of the device to be tested, associated supplies may be defined as described in Section 6.5.1.1. With associated supplies defined lines 1 to N of Table 2A may be used. The additional information required for Table 2A allows the major current paths to be covered with fewer pin combinations saving test time and reducing potential overstress. Table 2A also eliminates non-supply to non-supply testing (i.e., I/O to I/O) except for special cases which are discussed in Section 6.3.3.1.

#### 6.3.1 No-Connect Pins

Verified no-connect pins must not be stressed and must be left floating at all times.

There are some pins which are labeled as no connect, such as thermal panels, which are actually connected to the die and should be classified as supply pin or non-supply pin as outlined below.

Pins labeled as no connect but found to have an electrical connection to the die shall be:

- Classified as a supply pin, if metallically connected to a supply pin.

- Classified as a non-supply pin, if not metallically connected to a supply pin.

#### 6.3.2 Supply Pins

A supply pin is any pin that provides current or a current return path to the circuit. While most supply pins are labeled such that they can be easily recognized as supply pins (examples: VDD, VDD1, VDD2, VDD\_PLL, VCC, VCC1, VCC2, VCC\_ANALOG, GND, AGND, DGND, VSS, VSS1, VSS2, VSS\_PLL, VSS\_ANALOG, etc.), others are not and require engineering judgment based on their function in the normal circuit operation (examples: Vbias, Vref, etc.). Supply pins typically transmit no information such as digital or analog signals, timing, clock signals, and voltage or current reference levels.

An example of a pin that appears to be a supply pin but may be treated as a non-supply pin is the VPP pin on EPROM memories. The VPP puts the memory into a special, rarely used, programming state and provides the high-voltage needed for programming the memory.

#### 6.3.2.1 Other Supply Pin Types

Any pin that is intended to be pumped above the positive supply or below the negative supply of its circuit block shall be treated as a supply pin (example: positive and negative terminal pins connected to a charge pump capacitor).

Any pin that is connected to an internal power bus (or a power pin) by metal as described in Section 6.3.2 shall be treated as a supply pin (example: a Vdd sensing pin).

Any pin that is intended to supply power to another circuit on the same chip must be treated as a supply pin. However, if a pin is intended to supply power to a circuit on another chip but not to any circuit on the same chip, it may be treated as a non-supply pin.

## 6.3.3 Non-Supply Pins

All pins not categorized as supply pins or no connects are non-supply pins. This includes pins such as input, output, offset adjusts, compensation, clocks, controls, address, data, Vref pins and VPP pins on EPROM memory. Most non-supply pins transmit or receive information such as digital or analog signals, timing, clock signals, and voltage or current reference levels.

## 6.3.3.1 Direct Coupled Non-Supply Pin Pairs

A coupled non-supply pin pair may have a potential ESD current path that does not involve supply rails. They include analog and digital differential pairs and other special function pairs (e.g., D+/D-, XTALin/XTALout, RFin/RFout, TxP/TxN, RxP/RxN, CCP\_DP/CCN\_DN etc.). Coupled non-supply pin pairs are device specific and not all devices will have them.

- Any non-supply pin pairs that may have current paths between them that does not involve the supply rails. This path may be through functional devices or through parasitic paths.

- Non-supply pin pairs directly interfacing with each other, such as differential inputs or differential outputs.

- Non-supply pin pairs that have a current path between them that consists of a single transistor or capacitor.

NOTE: Engineering judgment should be used to identify all coupled non-supply pin pairs. See Annex D for a more extensive list of examples for coupled non-supply pins.

## 6.4 Pin Groupings

#### 6.4.1 Supply Pin Groups

The supply pins are partitioned into supply pin groups with each supply pin defined as a member of one and only one supply pin group. A supply pin that is not connected by metal to any other pins forms a single pin supply pin group. Supply pins that are interconnected by metal on the chip or within the package form a supply pin group. The metal interconnects should be verified through reliable device documentation. However, excessive metal trace resistance in the die interconnect associated with grouping these pins could lead to masking an ESD protection weakness in HBM testing.

NOTE: If the pin interconnect design is unknown, either measure the resistance between supply pins to determine the supply pin groups or treat each pin as a separate supply pin group.

NOTE: If the resistance between any two pins is greater than 3 ohms, the pins should be placed into separate supply pin groups. The resistance is measured between any two supply pins with the same name. If there are more than two pins, then the worst case resistance should be determined by measurement.

## 6.4.1.1 Partitioning Supply Pin Groups

Pins of a supply pin group may be divided into two or more subgroups such that each pin is a member of at least one subgroup. This partitioning may result in each pin being in its own subgroup. When a supply pin group is being connected to Terminal B, all pins specified for Terminal A are stressed separately to each subgroup. When dividing a supply pin group into subgroups, all the subgroups remain part of their supply pin group and are not tested against each other.

#### 6.4.1.2 Supply Pins Connected by Package Plane

If a set of supply pins are connected by a package plane, as few as one pin (selected arbitrarily) from that set of pins may be used to represent the entire set as a supply pin group. The remaining pins in the set need not be stressed nor grounded and may be left floating during all testing.

NOTE: For example, if a supply pin group of 25 pins consists of five pins connected by metal only at the die level and 12 additional pins connected with one package plane and another with eight pins connected with a second package plane, the group may be represented by the five die-level connected pins and at least one pin from each package plane connected sets.

NOTE: Tester parasitics may be reduced by connecting all the pins of the group to Terminal B instead of leaving the unselected pins floating. This is not necessary if a custom board has been built which isolates the unselected pins.

## 6.4.1.3 Supply Pins Connected by an Above Passivation Layer

If a set of supply pins are connected by an above passivation layer (APL), as few as one representative pin(s) from that set of supply pins may be used to represent the entire set as the supply pin group. The remaining unselected pins in the set need not be stressed nor grounded and may be left floating during all testing as long as all such unselected pins are connected by the APL with a resistance of 1 ohm or less to any other pin in the set.

#### 6.4.2 Shorted Non-Supply Pin Groups

Shorted non-supply pins that are connected by metal in a package plane, an APL with a resistance less than 1 ohm and/or a common bond pad, form a non-supply pin group. One pin of this non-supply pin group (selected arbitrarily) may be used to represent the entire set of shorted non-supply pins. The remaining pins in the set need not be stressed nor grounded and may be left floating during all testing.

NOTE: This configuration is uncommon as non-supply pins typically are isolated from other pins in the package.

#### 6.5 Pin Stress Combinations

Table 2A lists the preferred set of pin combinations required for device classification. Alternatively, Table 2B can be used, which has the pin combination sets as required in ANSI/ESDA/JEDEC JS-001-2010. Furthermore, device stressing can be done using a combination of Table 2A and Table 2B. For example, one could use pin combination set 1 through N from Table 2A and set N+1 from Table 2B. Additional information and guidance on the use of the pin combinations are given in Annexes A and C. The test results, actual pin combination sets used, the tester(s) used and all tester settings necessary to reproduce the test shall be recorded and maintained according to company recordkeeping procedures.

Active discrete devices (FETs, transistors, etc.) shall be tested using all possible pin-pair combinations (one pin connected to Terminal A, another pin connected to Terminal B) regardless of pin name or function. Integrated circuits with ten pins or less may be tested with all pin-pair combinations.

Device stressing can be divided between two or more simulators if all simulators meet the requirements of Section 5.0 and all intended pin combinations are stressed.

**Table 2A. Required Pin Combinations Sets**

| Pin<br>Combination<br>Set Number<br>[Note A] | Pin(s) Connected to Terminal B<br>(Ground)                          | Pin Connected to Terminal A (Single Pins, tested one at a time)                                                                           |

|----------------------------------------------|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                            | Supply Pin Group 1 [Notes B and C]                                  | Every Supply Pin except pins of Supply Pin Group 1 [Notes C and D] Every Non-Supply Pin Associated with Supply Pin Group 1 (See Annex C)  |

| 2                                            | Supply Pin Group 2<br>[Notes B and C]                               | Every Supply Pin except pins of Supply Pin Group 2 [Notes C and D] Every Non-Supply Pin Associated with Supply Pin Group 2 (See Annex C)  |

|                                              |                                                                     |                                                                                                                                           |

| N                                            | Supply Pin Group N [Notes B and C]                                  | Every Supply Pin except pins of Supply Pin Group N [Notes C and D]  Every Non-Supply Pin Associated with Supply Pin Group N (See Annex C) |

| N+1                                          | One Pin of Each Coupled Non-<br>Supply Pin Pair, one pair at a time | The other pin of the Coupled Non-<br>Supply Pin Pair                                                                                      |

### NOTES:

- [A] In all combinations, pins not connected to either Terminal A or Terminal B shall be left unconnected (Floating Pins) during the stress pulse. All no-connect pins are unconnected at all times.

- [B] Supply pins may be all connected together as a single group, or divided into subgroups. Subgroups can be individual pins. Every Terminal A pin is stressed to each of these subgroups (see Section 6.4.1).

- [C] A single pin may be used from supply pin groups known to be interconnected by a package plane or APL (see Sections 6.4.1.2 and 6.4.1.3).

- [D] Supply pin-to-supply pin combinations may be stressed using only single polarity pulses (see Section 6.5.1.2).

Table 2B. Legacy Pin Combinations Sets (Equivalent to Table 2 of ANSI/ESDA/JEDEC JS-001-2010 which is shown in Annex F)

| Pin<br>Combination<br>Set Number<br>[Note CC] | Pin(s) Connected to Terminal B               | Pin Connected to Terminal A (Single Pins, tested one at a time)                            |

|-----------------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------|

| 1                                             | Supply Pin Group 1<br>[Note AA]              | Every Supply Pin except pins of Supply Pin Group 1 [Note AA]  Every Non-Supply Pin         |

| 2                                             | Supply Pin Group 2<br>[Note AA]              | Every Supply Pin except pins of Supply Pin Group 2 [Note AA]  Every Non-Supply Pin         |

|                                               |                                              |                                                                                            |

| N                                             | Supply Pin Group N<br>[Note AA]              | Every Supply Pin except pins of<br>Supply Pin Group N<br>[Note AA]<br>Every Non-Supply Pin |

| N+1                                           | All Non-supply Pins, except PUT<br>[Note BB] | Each Non-Supply Pin<br>(as the PUT)                                                        |

#### NOTES:

[AA] A single pin may be used from supply pin groups known to be interconnected by a package plane or APL (See Sections 6.4.1.2 and 6.4.1.3).

[BB] Non-supply pins connected to Terminal B can be divided into subsets, such that each of these pins is a member of at least one subset. Every Terminal A pin is stressed to each of these subsets.

[CC] All pins not connected to either Terminal A or Terminal B shall be left unconnected (floating pins) during the stress pulse. All no-connect pins are unconnected at all times.

## 6.5.1 Non-Supply and Supply to Supply Combinations (1, 2,... N)

Tables 2A and 2B are organized by the DUT's N supply pin groups. The first N rows of these tables have one unique supply pin group tied to Terminal B. When pins are not connected by a package plane, pins within a supply pin group shall be stressed individually (when connected to Terminal A). When tied to Terminal B, as shown in tables, these pins shall all be connected either individually, or in groups, or tied together at the test board level.

#### 6.5.1.1 Association of Non-Supply Pins with Supply Pin Groups (Table 2A only)

Each non-supply pin is associated with one or more supply pin groups (Section 6.4.1). For example, for an I/O pin, the output drivers of the pin connect to the VCCIO supply group while the input receiver of the same pin connects to the VCC supply group. Additionally, this I/O pin may be

connected to one or more grounds (e.g., VSS, VSSIO). This information is typically provided by the design team.

A non-supply pin is associated with a supply pin group if either:

- a) The connection to that supply pin group is necessary for the function of the circuit.

- b) A parasitic path exists between non-supply and supply pin group (e.g., open-drain type non-supply pin to a VCC supply pin group that connects to a nearby N-well guard ring).

In the testing described in Table 2A, non-supply pins are only stressed against the supply pin groups with which they are associated. If the information on the association with supply pin groups for each non-supply pin is known, then non-supply pins may be stressed only to their associated supply pin groups (see Annex C). Stressing to supply pin groups not associated with a non-supply pin is not required. If this information is not available, then every non-supply pin shall be tested to each supply pin group as specified in lines 1 to N of Table 2B.

NOTE: The use of Table 2A is highly recommended for devices exceeding eight supply pin groups.